一、数据的表示

1、R进制转10进制

2、10进制转R进制

例子:94 转二进制

2| 94 0

2| 47 1

2| 23 1

2| 11 1

2| 5 1

2| 2 0

2|1

(1011110)2

3、二进制转8进制、16进制

8进制

10 001 110

2 1 6

(216)8

O 216

16进制

1000 1110

8 E

(8E)16

OX8E

8EH

10 A 1010

11 B 1011

12 C 1100

13 D 1101

14 E 1110

15 F 1111

4、原码、反码、补码

假设 8 位

| 数值1 | 数值-1 | 1-1(1+(-1)) | |

|---|---|---|---|

| 原码 | 0000 0001 | 1000 0001 | 1000 0010 = -2 |

| 反码 | 0000 0001 | 1111 1110 | 1111 1111 = -127 |

| 补码 | 0000 0001 | 1111 1111 | 0000 0000 = 0 |

| 移码 | 1000 0001 | 0111 1111 | 1000 0000 = -0 |

1)8位 = 1位符号位+7位数据

2)正数的 原码、反码、补码都一样

3)负数的反码,除符号位,原码的基础上,取反

4)负数的补码,除符号位,原码的基础上,取反加1

5)移码,无论正负数,补码的基础上,符号位取反

6)补码0 有一个,原码和反码0 有两个(+-0)

5、小技巧

转成2进制

2^n = 1+n个0

2^n -1 = n个1

举例:

2^3 = 1000

2^3-1= 111

二、数值表示范围

| 码制 | 定点整数 | 定点小数 |

|---|---|---|

| 原码 | -2^(n-1) -1 ~ +2^(n-1) -1 | -(1-2^-(n-1)) ~ +1-2^-(n-1) |

| 反码 | -2^(n-1) -1 ~ +2^(n-1) -1 | -(1-2^-(n-1)) ~ +1-2^-(n-1) |

| 补码 | -2^(n-1) ~ +2^(n-1) -1 | -1 ~ +1-2^-(n-1) |

| 移码 | -2^(n-1) ~ +2^(n-1) -1 | -1 ~ +1-2^-(n-1) |

三、浮点数的运算

1、浮点数的表示

N = 尾数*基数^指数(阶)

2、运算过程

对阶 > 尾数计算 > 结果格式化

3、特点

1)一般尾数用补码,阶码用移码

2)阶码的位数,决定数的表示范围,位数越多范围越大

3)尾数的位数,决定数的有效精度,位数越多精度越高

4)对阶时,小数向大数看齐

5)对阶时,较小数尾数右移实现

4、浮点数存储的格式

| 阶符 | 阶码 | 数符 | 尾数 |

|---|---|---|---|

四、计算机结构

输入设备、辅助存储器、 输出设备 外设

主存储器 主机

运算器、控制器 CPU

1、运算器

1)算术逻辑单元 ALU :数据的算术运算和逻辑运算

2)累加寄存器 AC :通用寄存器,为ALU提供一个工作区,用在暂存数据

3)数据缓冲寄存器 DR :写内存时,暂存指令或数据

4)状态条件寄存器 (也可算作控制器)PSW :存状态标志和控制标志

2、控制器

1)程序计数器 PC :存储下一条要执行指令的地址

2)指令寄存器 IR :存储即将执行的指令

3)地址寄存器 DR

4)指令译码器 ID :对指令中的操作码字段进行分析解释

5)时序部件 :提供时序控制信号

五、计算机体系结构分类-Flynn

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能,至少不实际 | 目前没有,有文献称流水线计算机为此类 |

| MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、指令等全面执行 | 多处理机系统 多计算机 |

六、指令的基本概念

1、指令定义

一条指令就是机器语言的一个语句,它是一组有意义的二进制代码,

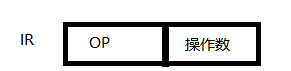

2、指令格式

3、操作码

4、地址码

5、分类

1)三地址指令

| OP | A1 | A2 | A3 |

|---|---|---|---|

2)二地址指令

| OP | A1 | A2 |

|---|---|---|

3)一地址指令

| OP | A1 |

|---|---|

4)零地址指令

| OP |

|---|

例如:宕机

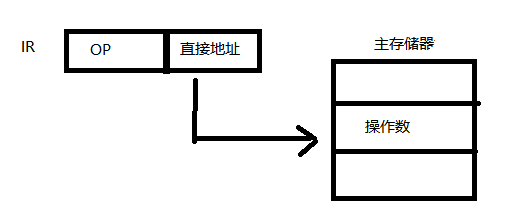

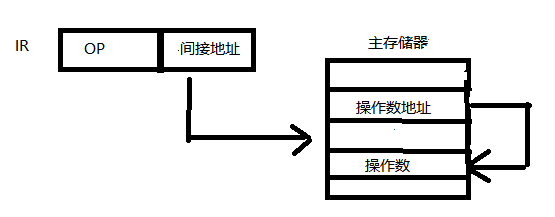

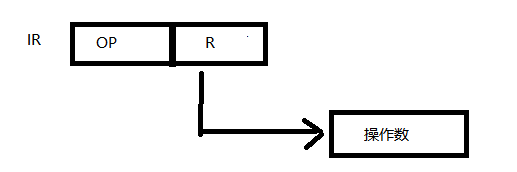

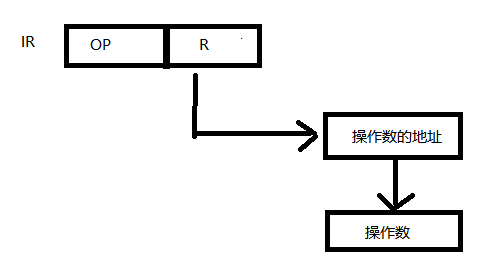

七、寻址方式

1、立即寻址方式

2、直接寻址方式

3、间接寻址方式

4、寄存器寻址方式

5、寄存器间接寻址方式

寄存器内存存放的是操作数地址

八、CISC 与 RISC

| 指令系统类型 | 指令 | 寻址方式 | 实现方式 | 其他 |

|---|---|---|---|---|

| CISC(复杂) | 数量多, 使用频率差别大, 可变长格式 |

支持多种 | 微程序控制技术(微码) | 研制周期长 |

| RISC(精简) | 数量少, 使用频率接近, 定长格式, 大部分为单指令周期, 操作寄存器,只有Load/Store操作内存 |

支持方式少 | 增加了通用寄存器 硬布线逻辑为主, 适合采用流水线 |

优化编译,有效支持高级语言 |

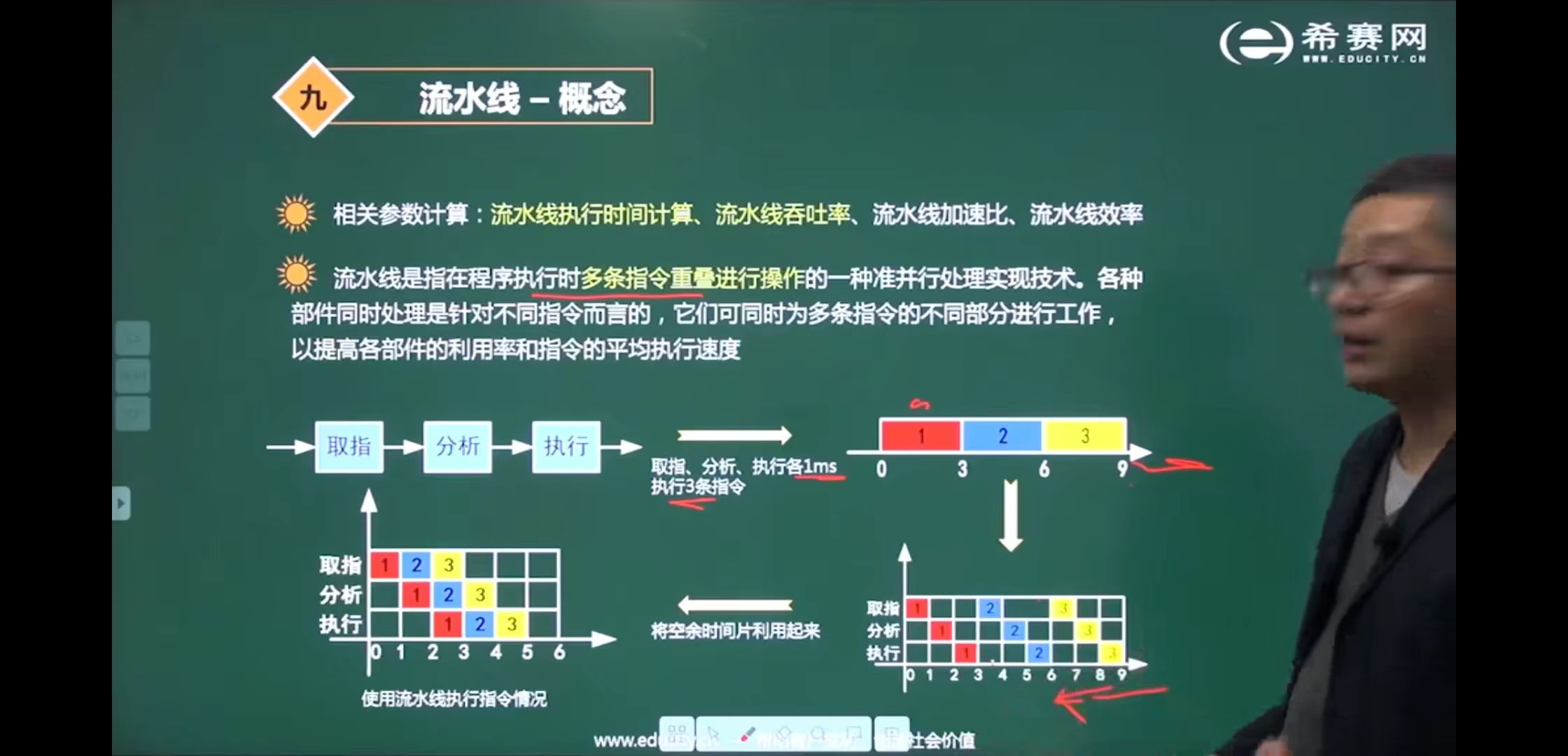

九、流水线

1、例子

假设指令执行时间都是 1ms

1)串行

取指 —> 分析 —> 执行 3ms

那3条指令就是 9ms

2)流水线

3条指令 5ms

2、流水线执行时间计算

1)流水线周期

2)计算公式

1条指令执行时间 + (指令条数-1)流水线周期

理论公式:(t1+t2+ …+ tk)+ (n-1)dt

实践公式:kdt + (n-1)dt

例题:

假设一条执行的执行过程可以分解为取指、分析、执行三步,

取指时间:3dt

分析时间:2dt

执行时间:4dt

问题1:若按串行方式执行,则10条指令执行完毕,需要多少dt

问题2:若按流水线方式执行,流水线周期为 多少dt,则10条执行完毕,需要多少dt

答:

问题1:all = (3+2+4)10 = 90 dt

问题2:

流水线周期= 4 dt

理论:all = (3+2+4)+(10-1)4 = 9+ 94 = 45 dt

实践:all = 34 + (10-1)*4 = 12 + 36 = 48 dt

3、超标量流水线

类比:多条流水线,几条就是几度

假设是2度,那么10条指令的执行时间,其实是5条指令(10/2)执行的时间

4、流水线吞吐率计算

1)定义,Though Put rate ,TP,指在单位时间内流水线所完成的任务数量 或输出的结果数量

2)公式:

TP = 指令条数/流水线执行时间

3)流水线最大吞吐率 = 1/dt(流水线周期)

5、流水线的加速比

6、流水线的效率

十、层次化存储结构

速度快(容量小)CPU 寄存器、最快、容量小、成本高

Cache 按内容存取

内存(主存) 分两类(随机存储器RAM、只读存储器ROM)

速度慢(容量大)外存(辅存) 硬盘、光盘、U盘等

十一、Cache

1、原理

使用cache改善系统性能的依据是 程序的局部性原理(时间局部性、空间局部性,防止抖动)

2、命中/失效

CPU访问这个数据,查找的数据正好在cache里,说明是命中了,不在就是失效了

3、计算

h :cache的命中率

t1 :cache的周期时间

t2 :主存储器周期时间

以读操作为例,使用”cache+主存储器” 的系统平均周期为t3

t3 = ht1+ (1-h) t2

4、映象

1)直接映象

硬件电路较为简单、但冲突率很高

cache 0 页只能存主存里面 0页的内容

主存标记、cache页号、页内地址

2)全相联映象

电路难于设计和实现,只适用于小容量的cache,冲突率较低

主存标记、页内地址

3)组相联映象

直接和全相联的折中

组内用全相连,组外用直接

十二、主存、编址与计算

1、存储单元

1)按字(bit)编址:存储体的存储单元是 字存储单元,即最小的寻址单位为一个字

2)按字节(Byte)编址:存储体的存储单元是 字节存储单元,即最小的寻址单位为一个字节

1Byte = 8 bit

2、计算

3、例题

若内存地址区间为 4000H ~ 43FFH,每个存储单元可存储 16位2进制数,

该内存区域用 4片存储器芯片构成,则构成该内存所用的存储器芯片的容量是多少

答:

1)存储单元个数 = 43FFH - 4000H +1 = 400H

2)400H =(0100 0000 0000)2 = 2^10

16进制 2进制 10进制

3)总存储器的容量 = 2^10 x 16 bit

4)每片芯片容量= 总容器容量/芯片数 = 2^10 x 16 bit / 4 = 256x 16bit

4、主存-分类

随机存取存储器(RAM)

SDRAM 动态RAM

SRAM 静态RAM

只读存储器(ROM)

BIOS

5、编址

十三、总线

1、数据总线

Data Bus,在CPU与RAM之间来回传递需要处理或 需要存储的数据

2、地址总线

3、控制总线

Control Bus,将微处理器控制单元的信号,传送到周边设备,一般为USB bus 和1394 bus

十四、串联与并联系统(可靠性)

十五、N模混合系统

串1 —- 》并1 —- 》并1

并2 并2

并3

Rx (1-(1-R)^3)x(1-(1-R)^2)

十六、校验码

1、奇偶校验

2、循环冗余校验

1)可检错,不可纠错

2)例题:

原始报文为 11001010101

多项式为 x^4+x^3+x+1

对其进行CRC编码,结果为?

解:

1)多项式转换成二进制为 11011

2)原始报文 转换为 11001010101 + 0000 (多项式位数减一)

3)进行异或相除

110010101010000

11011 —

00010010

11011 —

010011

11011 —

010000

11011 —

010111

11011 —

011000

11011 —

00011000

11011 —

00011 — 余数

4)再把得到的余数4位,替换掉刚才报文补的4个0,得到CRC编码

11001010101+0011

5)再把 4)中的报文 对 多项式 11011进行模2 ,得到余数 为0 ,即正确

3、海明校验

可检错、可纠错

2^r -1 >= m+r

r是校验位