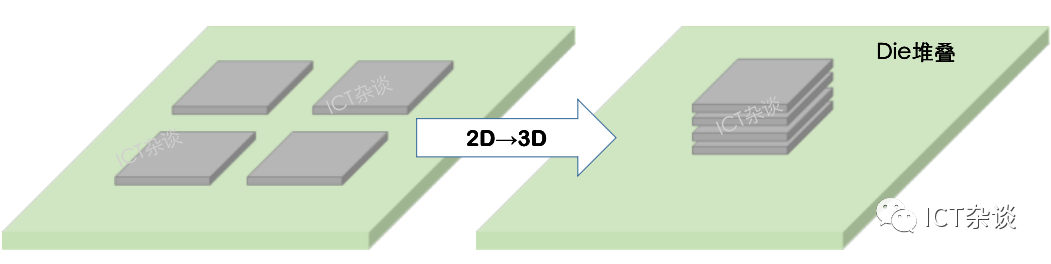

随着摩尔定律速度放缓,为了继续提升设备性能,ICT行业转向了3D芯片堆叠互连技术,这样,既可以增加芯片之间的带宽,又能改善计算性能。然而,芯片的堆叠对散热却带来了极大的挑战,因为在一个芯片堆叠内的多个Die,导致热量堆积,单位面积的热流密度大大提升,如果不能通过有效的手段进行散热,必然会导致芯片热可靠性出现问题。

图1 2D→3D芯片封装示意

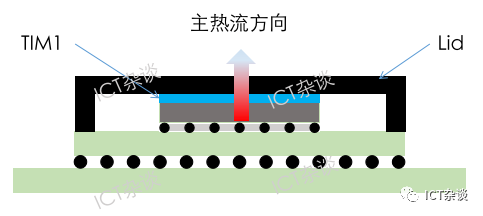

如图2所示,是一个典型的2D封装芯片示意图,该芯片的主热量方向是向上,也就是我们常说的Top面/Case面。封装内Die和封装外壳Lid之间有一层导热材料,一般我们称为TIM1。

图2 2D封装示意图

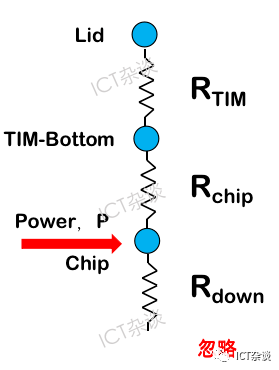

如图3所示,在2D封装中,热阻主要有芯片自身的热阻Rchip、芯片和Lid之间的界面热阻RTIM,以及有极少量热量传递的向下的热阻Rdown。因此,对于2D封装,从改善散热角度,可以通过降低RTIM或去掉Lid减少Lid产生的热阻来进行。

图3 2D封装热阻示意图

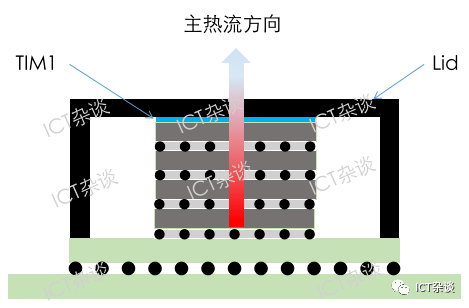

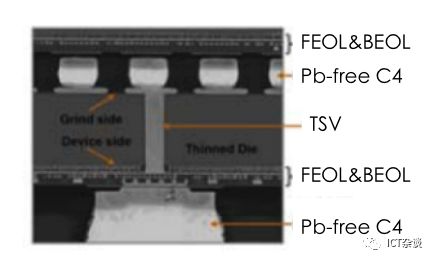

如图4所示,这是一个典型3D封装示意图,芯片Die堆叠,使得热量通过多个Die传导。芯片中的第n个Die产生的热量将通过N-1个Die传导热量,到达位于芯片组中最后上面一个Die顶部的散热器或冷板。初次之外,需要注意的是,Die包括复杂的结构,包括前端工艺线路层(FEOL)、后端工艺线路层(BEOL),以及通过硅通孔与uC4相互连接,如图5所示。这些堆叠、封装结构会存在一些公差,大幅增加堆叠Die和顶部Die上面安装的散热器/冷板之间的热阻。

图4 3D封装示意图

图5 示意图

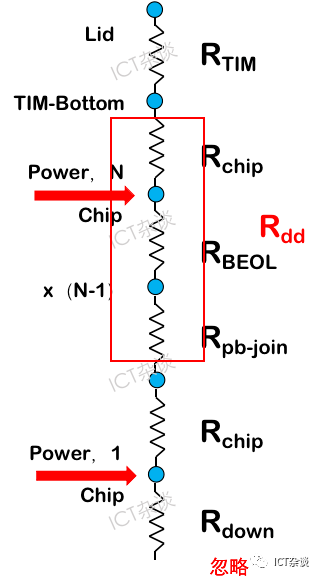

如图6所示,在3D封装中,热阻主要有芯片自身的热阻Rchip、芯片和Lid之间的界面热阻RTIM,以及有极少量热量传递的向下的热阻Rdown。其中芯片自身的热阻包含了多个Die以及Die之间各种工艺如焊球、TSV、复杂走线层等等构成的热阻Rdd。这样的话,要提升3D封装的散热效果,除了像2D封装一样降低RTIM、取消Lid外,Rdd的降低是非常重要的。

图6 3D封装热阻示意图然而,通过改善芯片封装自身的热阻是非常有限的,更大的压力还是落在系统设计上,寻求解决热流密度更高的热设计方案是未来系统热设计层面最重要的事情。风冷即将达到极限,封装级甚至进入封装内部的液冷方案将在未来成为超高功耗、超高热流密度先进封装技术下的主流散热解决方案。