AT89S52引脚按功能可分为三类:电源及时钟引脚 Vcc、Vss;XTAL1、XTAL2

控制引脚(不会输入上划线,只能用”“啦)PSEN、ALE/PROG、EA/Vpp、RST

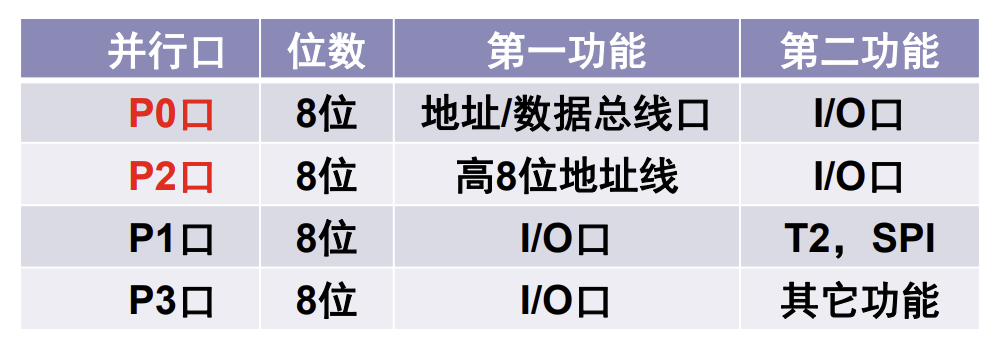

I/O口引脚 P0、P1、P2、P3,为4个8位并行I/O口的外部引脚

电源及时钟引脚Vcc(40引脚) 接+5V电源

Vss(20引脚) 接数字地

XTAL1(19引脚) 片内时钟震荡器反相放大器的输入端。当使用AT89S52单片机片内的时钟振荡器时,该引脚外接石英晶体和微调电容。当使用外部独立时钟振荡器时,该引脚接独立时钟振荡器的输出信号。

XYAL2(18引脚) 片内时钟振荡器反相放大器的输出端。当使用片内时钟振荡器时,该引脚外接石英晶体和微调电容。当使用片外独立的时钟振荡器时,XTAL2引脚应该悬空。

控制引脚RET(RESET, 9引脚) 复位信号输入端,高电平有效。在此引脚上加上持续时间大于2个机器周期的高电平,就可以使单片机复位。单片机正常工作时,此引脚应为小于等于0.5V的低电平。当看门狗定时器溢出时,在引脚内部,看门狗定时器向该引脚输出长达96个时钟振荡周期的高电平,从而使单片机复位。

EA/Vpp(enable address/ voltage pulse of programming, 31引脚)

EA(enable address)为该引脚的第一功能,外部程序存储器访问允许控制端。

EA=1时,在AT89S52单片机内的PC[1]值(Program Counter,程序计数器)不超出1FFFH(即不超过片内8KB程序存储器的最大地址)时,AT89S52单片机读片内程序存储器(8KB)中的程序代码,但PC值超出1FFFH(即超出片内8KB Flash存储器的最大地址)时,将自动转向读取片外60KB(2000H~FFFFH)程序存储器的程序代码。

EA=0时,单片机只读取外部程序存储器中的内容,读取的地址为0000H~FFFFH,此时片内的8KB Flash程序存储器不起作用。

Vpp为该引脚的第二功能,在对片内Flash进行编程时,该引脚接入编程电压。

ALE/PROG(address latch enable/ programming,30引脚)

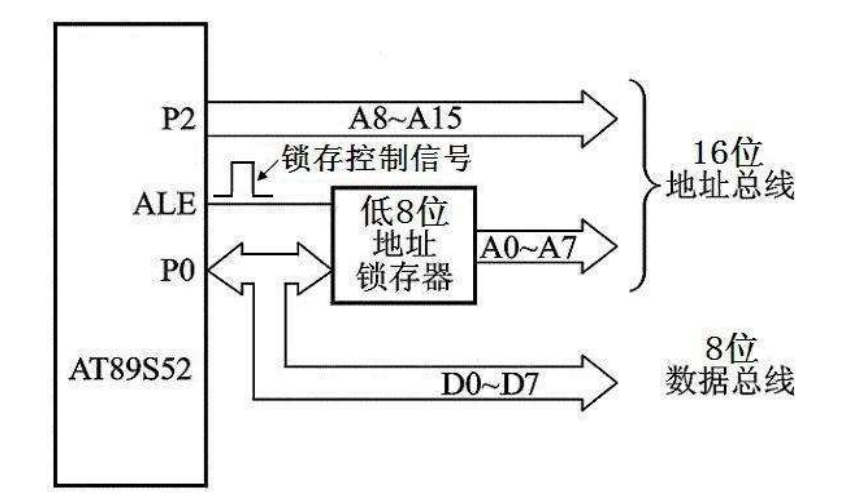

ALE为地址锁存控制信号端,是该引脚的第一功能。由于单片机的引脚数目有限,P0口是作为低8位地址总线与8位数据总线分用时复用的。当单片机访问外部程序存储器或者外部数据存储器时,ALE的负跳变将单片机P0口先发出的低8位地址锁存在P0口外接的地址锁存器中,然后P0口再作为8位数据总线使用。

此外单片机正常运行时,ALE端一直有正脉冲信号输出,此频率为时钟振荡器频率Fosc的1/6。该正脉冲信号可作外部定时或触发信号使用。但每当AT89S52执行访问外部RAM或I/O指令时,要丢失一个ALE脉冲。所以ALE引脚的输出信号频率并不是准确的Fosc/6。

若不需要ALE输出脉冲信号,可将特殊功能寄存器AUXR的第0位(ALE的禁止位)置1。但在访问外部RAM或外部ROM时,将ALE的禁止位置1,也不影响单片机对外部存储器的访问,ALE引脚仍有脉冲信号输出。

PROG为该引脚的第二功能,在对片内Flash程序存储器编程时,此引脚为编程脉冲的输入端。

PSEN(program strobe enable,29引脚)

访问片外程序存储器的读选通信号。当访问片外程序存储器读取指令码时,每个机器周期产生两次有效信号,即输出两个PSEN有效脉冲。在执行读取片内程序存储器指令码时不产生此脉冲,在读写外部数据存储器时也不产生PSEN_信号。 因此,外扩程序存储器时使用该脚。

**引脚P0口(P0.7~P0.0引脚)

为漏极开路的8位并行双向I/O口。作为输出口时,每个引脚可驱动8个LS型TTL[2]负载。当AT89S52扩展外部存储器及I/O接口芯片时,P0口为分时复用的低8位地址/数据总线。在向P0口写入1后就变成高阻态的输入口。

当P0口作为通用I/O口使用时,需外加上拉电阻,此时为准双向口。

对片内Flash程序存储器编程时,P0口接受字节代码,在程序校验时P0口输出字节代码,程序校验期间应外接上拉电阻。

P1口(P1.7~P1.0引脚)

准双向I/O口,具有内部上拉电阻,可驱动4个LS型TTL负载。

在对片内Flash编程和校检时定义为低8位地址线。

P1.0/T2 T2引脚为定时器/计数器T2的外部计数信号输入端

P1.1/T2EX T2EX为定时器/计数器T2的捕捉/重新装载出发及方向控制

P1.5/MOSI MOSI[3]用于对片内Flash存储器的串行编程和校验

P1.6/MISO MISO用于对片内Flash存储器的串行编程和校验

P1.7/SCK SCK为片内Flash存储器的串行编程和检验的移位脉冲输入引脚

P2口(P2.7~P2.0引脚)

准双向I/O口,引脚内部接有上拉电阻,可驱动4个LS型TTL负载。

当AT89S52访问外部存储器及I/O时,P2口作为高8位地址总线。当P2口不作为高8位地址总线时,可作为通用的I/O口使用。

P3口(P3.7~P3.0引脚)

准双向I/O口,引脚内部有上拉电阻。

P3口第一功能是作为通用的I/O口使用,可驱动4个LS型TTL负载。

P3口第二功能[4]:

引脚 第二功能 说明

P3.0 RXD 串行数据输入口

P3.1 TXD 串行数据输出口

P3.2 INTO 外部中断0输入

P3.3 INT1 外部中断1输入

P3.4 T0 定时器0外部计数输入

P3.5 T1 定时器1外部计数输入

P3.6 WR 外部数据存储器写选通控制信号

P3.7 RD 外部数据存储器读选通控制信号

综上所述,P0口作为地址总线(低8位)及数据总线使用时,为双向口;作为通用的I/O口使用时,需加上拉电阻,为准双向口。而P1口、P2口与P3口内部均有上拉电阻,所以均为准双向口,没有高阻“悬浮”态。

双向口P0与P1、P2、P3这三个准双向口相比,多了一个高阻“悬浮”的输入状态。这是由于P0作为数据总线使用时,多个数据源都挂在总线上,当P0口不需要与其他数据源打交道时,需要P0口与数据总线上的其他数据源高阻“悬浮”隔离。而准双向I/O口无高阻“悬浮”状态。另外,准双向口作通用I/O的输入口使用时,一定要向该口先写入1。