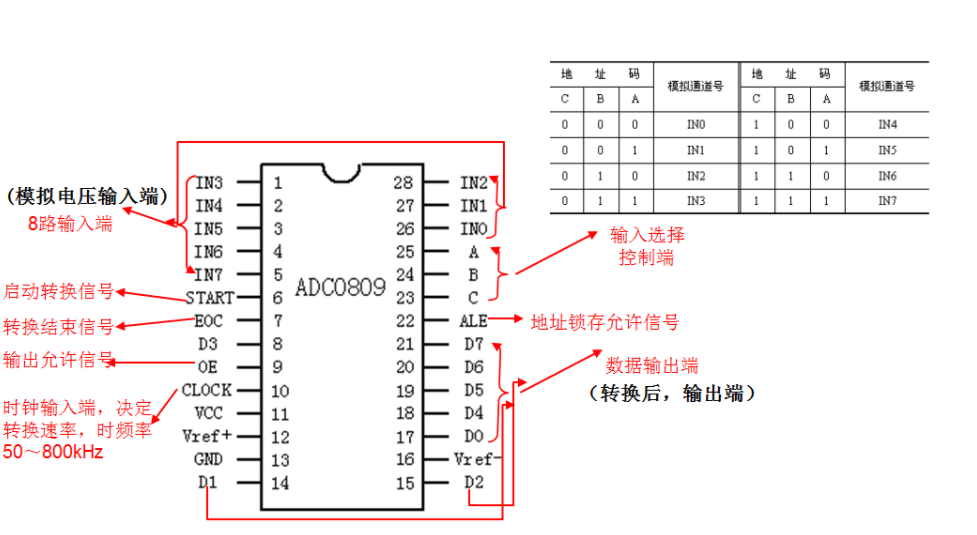

1.引脚功能

ADC0809芯片有28条引脚,采用双列直插式封装,如图13.23所示。下面说明各引脚功能。

IN0~IN7:8路模拟量输入端。

2-1~2-8:8位数字量输出端。

ADDA、ADDB、ADDC:3位地址输入线,用于选通8路模拟输入中的一路

ALE:地址锁存允许信号,输入,高电平有效。

START: A/D转换启动信号,输入,高电平有效。

EOC: A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低平)。

OE:数据输出允许信号,输入,高电平有效。当A/D转换结束时,此端输入一个高电平,才能打开输 出三态门,输出数字量。

CLK:时钟脉冲输入端。要求时钟频率不高于640KHZ。

REF(+)、REF(-):基准电压。

Vcc:电源,单一+5V。

GND:地。

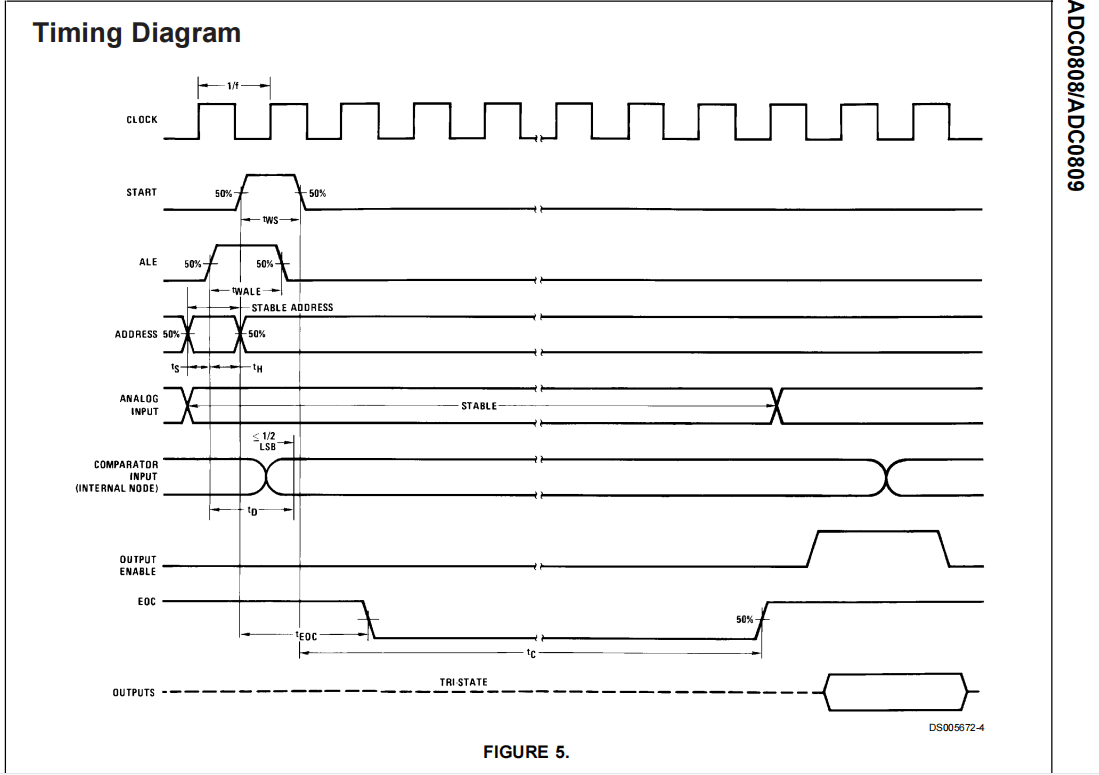

2.工作过程

1.ALE=0, START = 0;3位地址加一

2.输入3位地址,并使ALE=1,将地址存入地址锁存器中,经地址译码器译码从8路模拟通道中选通一路模拟量送到比较器。

3.送START一高脉冲,START的上升沿使逐次逼近寄存器复位,下降沿启动A/D转换,并使EOC信号为低电平。

4.当转换结束时,转换的结果送入到输出三态锁存器,并使EOC信号回到高电平,通知CPU已转换结束。

5.当CPU执行一读数据指令,使OE为高电平,则从输出端D0~D1读出数据。

3.编写verilog .v文件

/********************************************************************************名称 :verilog_second.v功能:仿真ADC0809 循环采集8个通道输入:clk500K,rst_n,EOC,[7:0] DATA,输出:START,OE, ALE,[2:0] ADDABC,[7:0] DATA_R作者:王世阳创建日期:2021.04.11修改日期1:修改内容1:*********************************************************************************/module verilog_second(input clk500K, // 时钟信号 (需要实物操作需要加锁相环分频)input rst_n, // 复位信号input EOC, //A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低平)。input [7:0] DATA, //8路adc转换好的数据的输入端。output reg START, //A/D转换启动信号,输入,高电平有效。output reg OE, //数据输出允许信号,输入,高电平有效。当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。output reg ALE, //地址锁存允许信号,输入,高电平有效。output reg [2:0] ADDABC, //3位地址输入线,用于选通8路模拟输入中的一路output reg [7:0] DATA_R //8位数字量所存输出端。);reg [2:0] ABC = 3'b000;//--内部端口声明reg[4:0] CS,NS;parameter IDLE=5'b00001,START_H=5'b00010,START_L=5'b00100,CHECK_END=5'b01000,GET_DATA=5'b10000; //五个状态//--逻辑功能实现always @(posedge clk500K)case(CS)IDLE:NS=START_H;START_H:NS=START_L;START_L:NS=CHECK_END;CHECK_END:if(EOC) //当EOC信号回到高电平,通知CPU已转换结束。NS=GET_DATA;elseNS=CHECK_END;GET_DATA:NS=IDLE;default:NS=IDLE;endcasealways@(posedge EOC)beginABC <= ABC + 3'b001;ADDABC <= ABC;endalways @(posedge clk500K or negedge rst_n) //如果复位电平来临回归起始状态beginif(!rst_n)beginCS<=IDLE;endelseCS<=NS;endalways @(posedge clk500K)case(NS)IDLE:begin //ALE=0, START = 0;3位地址加一OE<=0;START<=0;ALE<=0;endSTART_H:begin //输入3位地址,并使ALE=1,将地址存入地址锁存器中,经地址译码器译码从8路模拟通道中选通一路模拟量送到比较器送START一高脉冲,START的上升沿使逐次逼近寄存器复位,。OE<=0;START<=1; // 产生启动信号ALE<=1;endSTART_L:begin //START=下降沿启动A/D转换,并使EOC信号为低电平。OE<=0;START<=0;ALE<=1; //启动信号脉宽要足够长 ,在启动的时候 ALE要一直有效endCHECK_END:begin //当转换结束时,转换的结果送入到输出三态锁存器,并使EOC信号回到高电平,通知CPU已转换结束。OE<=0;START<=0;ALE<=0;endGET_DATA:begin //当CPU执行一读数据指令,使OE为高电平,则从输出端D0~D1读出数据。OE<=1; // 高电平打开三态缓冲器输出转换数据DATA_R<=DATA; //提取转换数据START<=0;ALE<=0;enddefault:beginOE<=0;START<=0;ALE<=0;endendcaseendmodule

4.编写verilog .vt文件

`timescale 1 ns/ 1 psmodule verilog_second_vlg_tst();// constants// general purpose registersreg eachvec;// test vector input registersreg clk500K;reg rst_n;reg EOC;reg [7:0] DATA;// wireswire START;wire OE;wire ALE;wire [2:0] ADDABC;wire [7:0] DATA_R;integer i;// assign statements (if any)verilog_second i1 (// port map - connection between master ports and signals/registers.clk500K(clk500K),.rst_n(rst_n),.EOC(EOC),.DATA(DATA),.START(START),.OE(OE),.ALE(ALE),.ADDABC(ADDABC),.DATA_R(DATA_R));initialbegin// code that executes only once// insert code here --> begin//#0 CLK_50M =1'b0; //时钟初始化为 1//#10000 rst_n =1'b0; //延时 10ns,低电平复位#0 clk500K =1'b0; //时钟初始化为 1#0 rst_n =1'b1;#0 EOC =1'b1;#0 DATA =1'b0;#10 EOC =1'b0;#2 DATA = DATA + 10;#2 EOC =1'b1;for(i = 0;i<80;i = i+1)begin#10 EOC =1'b0;#2 DATA = DATA + 10;#20 EOC =1'b1;end#30 $stop; //延时停止仿真// --> endendalways #1// optional sensitivity list// @(event1 or event2 or .... eventn)begin// code executes for every event on sensitivity list// insert code here --> beginclk500K=~clk500K;// --> endendendmodule

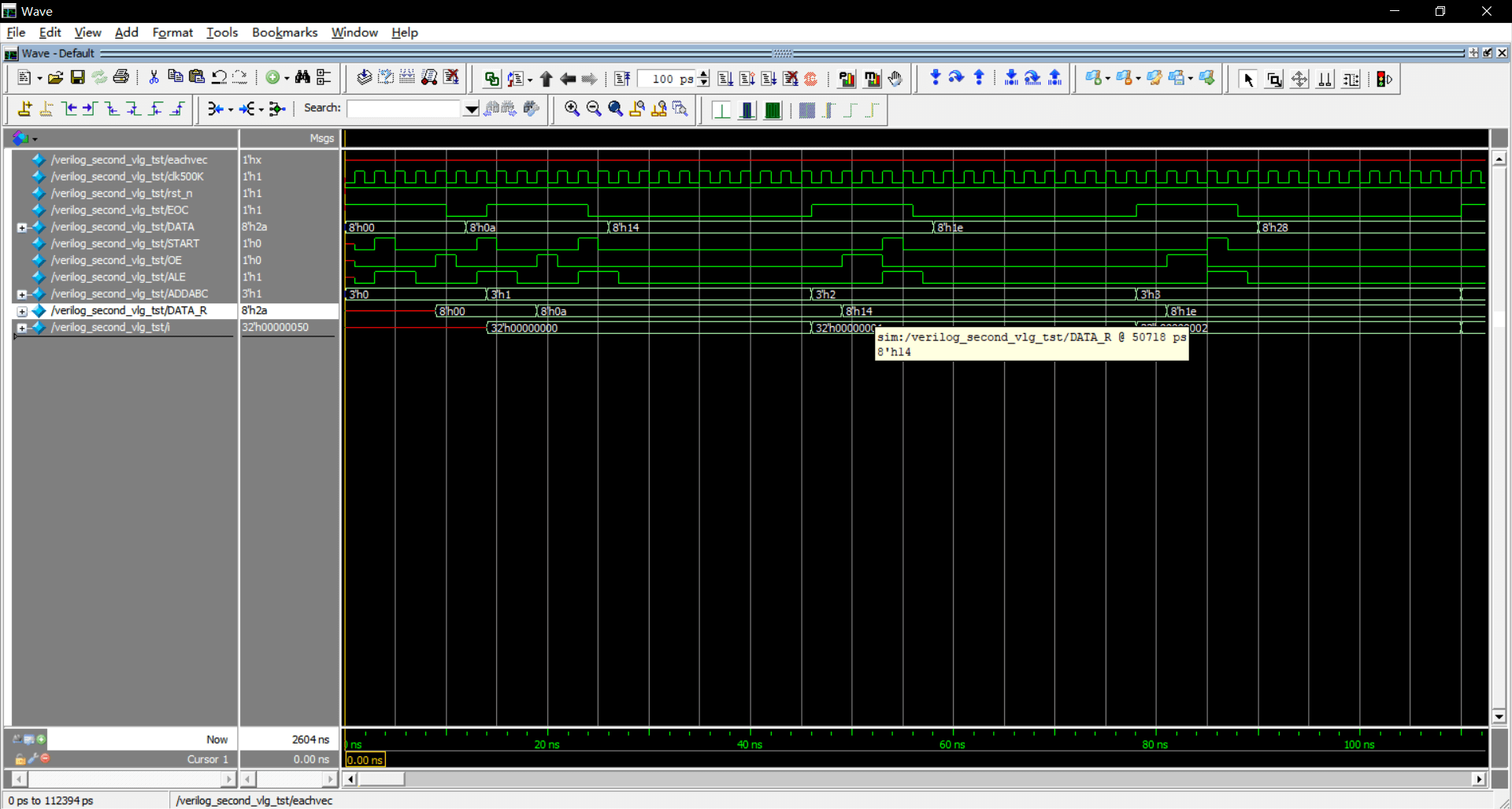

5.仿真效果图