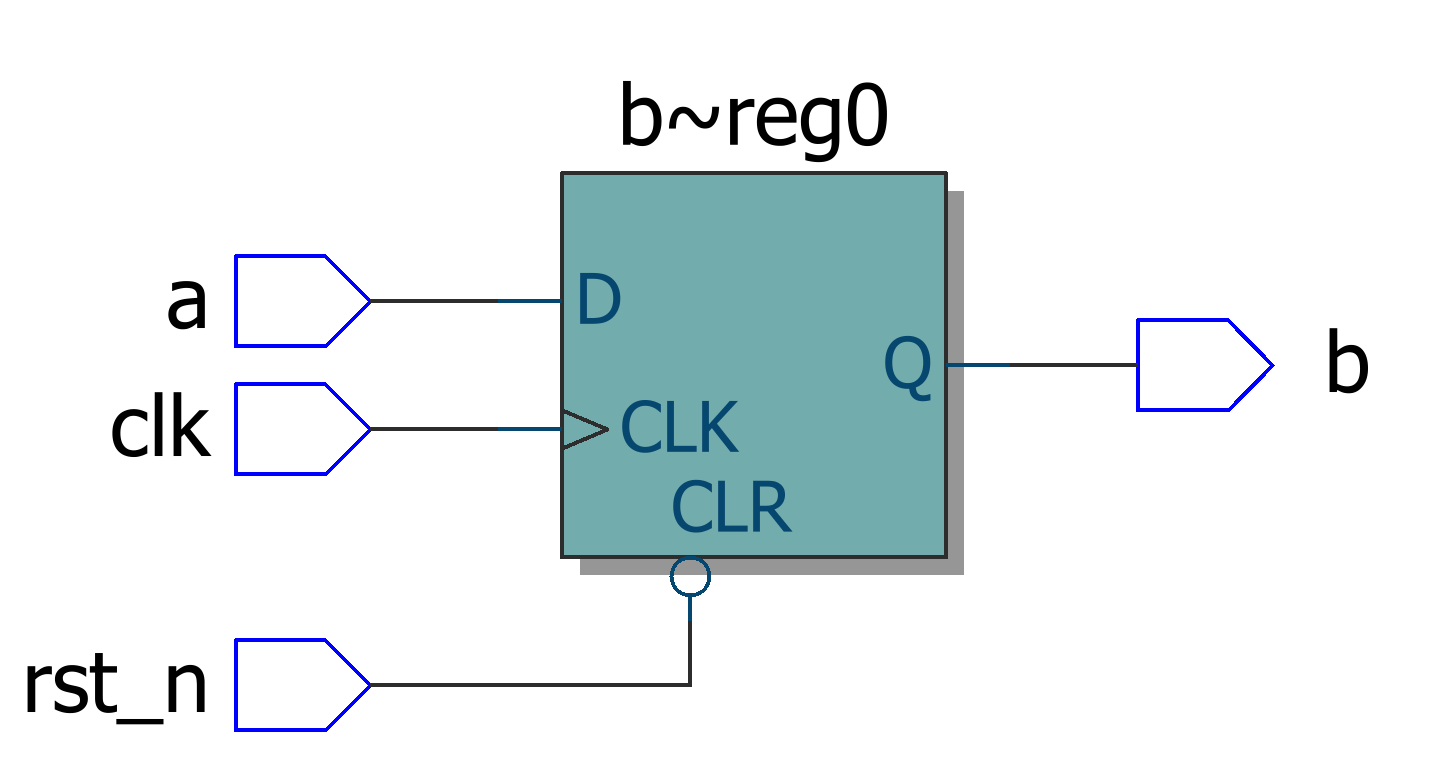

一、同步复位(by Crazybingo)

module system_ctrl//==================<端口>==================================================(//globel clock ----------------------------------input wire clk , //时钟,50Mhzinput wire rst_n , //复位,低电平有效//user interface --------------------------------input wire a , //输入信号output reg b //输出信号);//==========================================================================//== 同步复位,rst_n作为外部信号输入,clk全局时钟称为“同步时钟”//==========================================================================always @(posedge clk) beginif(!rst_n)b <= 0;elseb <= a;endendmodule

2.RTL视图

3.优点

①降低了亚稳态的出现概率;

②可以使所设计的系统成为100%的同步时序电路,这将大大有利于时序分析,并且综合出来的fmax一般较高;

③因为它只有在时钟有效沿到来时才有效,所以可以滤除高于时钟频率的毛刺。

4.缺点

①复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务,同时还要考虑clk skew、组合逻辑路径延时、复位延时等因素;

②由于大多数的逻辑器件的目标库内的DFF都只有异步复位端口,所以倘若采用同步复位,综合器就会在寄存器的数据输入端口插入组合逻辑,这样会耗费较多的逻辑资源。

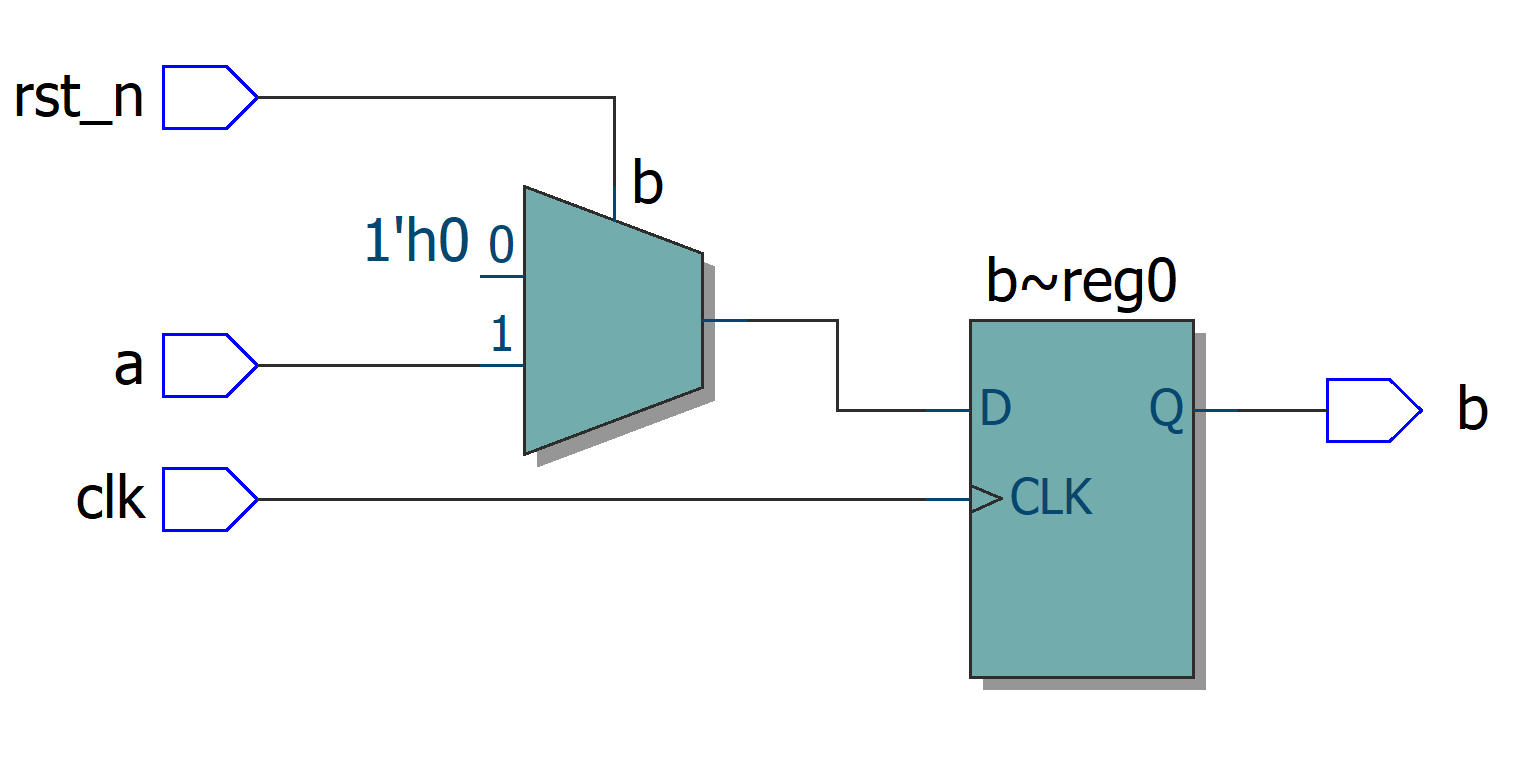

二、异步复位(by Crazybingo)

module system_ctrl//==================<端口>==================================================(//globel clock ----------------------------------input wire clk , //时钟,50Mhzinput wire rst_n , //复位,低电平有效//user interface --------------------------------input wire a , //输入信号output reg b //输出信号);//==========================================================================//== 异步复位,rst_n信号和clk全局时钟信号共同称为“异步时钟”//==========================================================================always @(posedge clk or negedge rst_n) beginif(!rst_n)b <= 0;elseb <= a;endendmodule

2.RTL视图

3.优点

①大多数目标器件的DFF都有异步复位端口,因此采用异步复位可以节省资源;

②设计相对简单;

③异步复位信号识别方便,并且可以很方便地使用FPGA的全局复位端口。

④推荐使用异步复位

4.缺点

①在复位信号释放(Release)时容易出现问题。具体来说,倘若复位释放时恰好在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致不稳定;

②复位信号容易受到毛刺的影响。这是由于时钟抖动或按键触发时的硬件原因造成的。

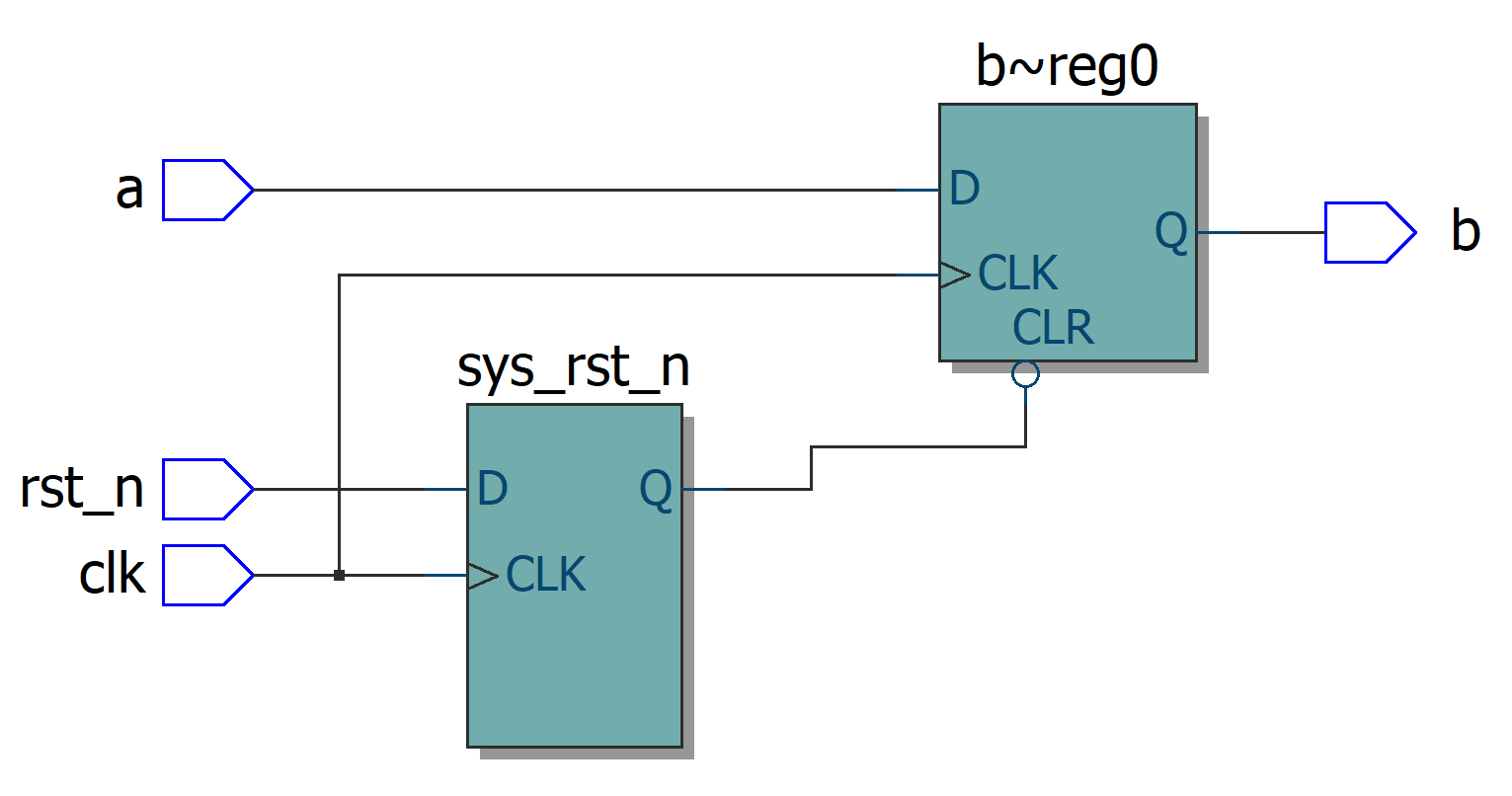

三、异步复位的同步化设计(by Crazybingo)**

module system_ctrl//==================<端口>==================================================(//globel clock ----------------------------------input wire clk , //时钟,50Mhzinput wire rst_n , //复位,低电平有效//user interface --------------------------------input wire a , //输入信号output reg b //输出信号);//==========================================================================//== 异步复位的同步化设计//==========================================================================reg sys_rst_n;always @(posedge clk) beginif(!rst_n)sys_rst_n <= 0;elsesys_rst_n <= rst_n;endalways @(posedge clk or negedge sys_rst_n) beginif(!sys_rst_n)b <= 0;elseb <= a;endendmodule

2.RTL视图

3.理解

①所谓“异步复位”是针对D触发器的复位端口,它是异步的,但是设计中已经同步了异步复位信号,所以笔者(Crazybingo)认为这只是某种意义上的“异步复位”。

②所谓“同步释放”,实际上是由于我们设计了同步逻辑电路,外部复位信号不会在出现释放时与clk信号竞争,整个系统将与全局时钟clk信号同步。

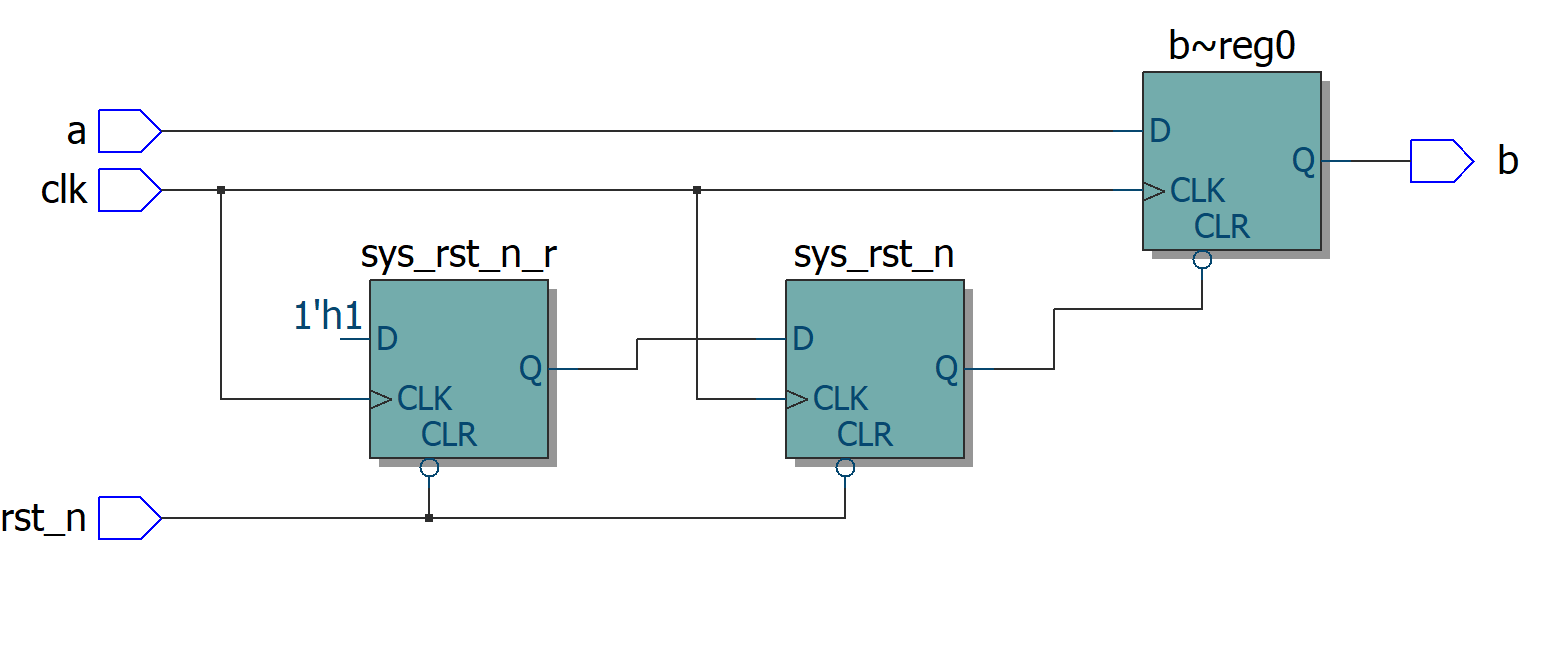

四、异步复位同步释放(by特权同学)

module system_ctrl//==================<端口>==================================================(//globel clock ----------------------------------input wire clk , //时钟,50Mhzinput wire rst_n , //复位,低电平有效//user interface --------------------------------input wire a , //输入信号output reg b //输出信号);//==========================================================================//== 异步复位的同步化设计//==========================================================================reg sys_rst_n_r;reg sys_rst_n;always @(posedge clk or negedge rst_n) beginif(!rst_n) beginsys_rst_n_r <= 0;sys_rst_n <= 0;endelse beginsys_rst_n_r <= 1;sys_rst_n <= sys_rst_n_r;endendalways @(posedge clk or negedge sys_rst_n) beginif(!sys_rst_n)b <= 0;elseb <= a;endendmodule

那我就奇怪了,Crazybingo和特权的,哪一个才是真正的“异步复位同步释放”呢?网上比较多的是特权同学这种,但Crazybingo的好像也没有什么错误。