Silicon Carbide MOSFET模块

对于一直在设法提高效率和功率密度并同时维持系统简单性的功率设计师而言,碳化硅SiC MOSFET的高开关速度、高额定电压和小RDS(on)使得它们具有十分高的吸引力。然而,由于高开关速度会导致高漏源电压(Vds)峰值和长振铃期,它们会产生电磁干扰,尤其是在电流大时。本文提供了一个较好的解决方案来优化电磁干扰和效率之间的平衡。这种方法已经采用1200V 40mOhm器件进行了双脉冲测试验证。

Vds峰值和振铃

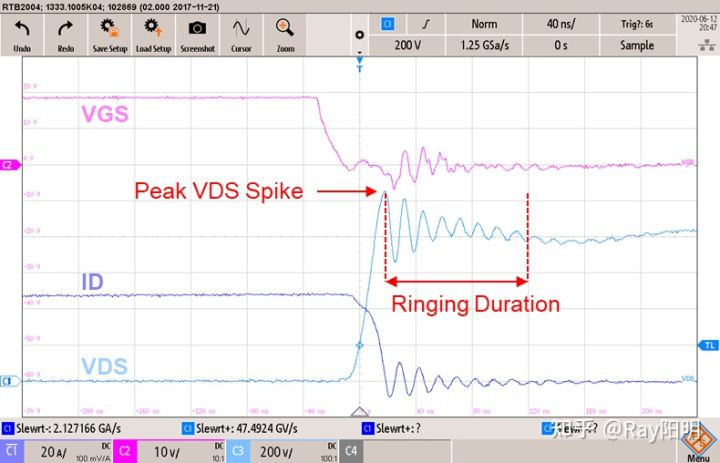

寄生电感是SiC MOSFET的VDS峰值和振铃的主要成因。从关闭波形(图1)中看,栅源电压(VGS)从18V至0V。关闭时的漏极电流(ID)为50A,VDS为800V。SiC MOSFET的高开关速度会导致高VDS峰值和长振铃期。该峰值降低了器件的设计余量以应对照明条件或负载突变,而长振铃期则带来的电磁干扰。在大电流下,这种情况更加明显。

图:使用SiC MOSFET时在关闭情况下的VDS峰值和振铃(1200V,40mOhm)

电磁干扰抑制技术

传统的电磁干扰抑制方法是使用大栅极电阻(RG)降低电流流经器件的速度(dI/dt)。但是大RG会显著增加开关损耗,要在效率和电磁干扰之间进行权衡取舍。

另一种抑制电磁干扰的方法是降低功率回路杂散电感。要实现这一目的,需要更改电路板的布局,还需要使用体积较小、电感较低的封装。然而,尽量降低功率回路的效果是有限的,而且还需要遵守最小空隙和间隔方面的安全规定。使用较小的封装也会影响热性能。

可以使用过滤器来帮助达到电磁干扰要求,简化系统权衡。频率抖动等控制技术也能降低供电导致的电磁干扰噪音。

使用RC缓冲电路

采用简单的RC缓冲电路是一种更为有效和高效的方法。它能控制VDS峰值并缩短振铃期,同时实现更高的效率和可以忽略的关闭延迟。由于更快的dv/dt和额外的电容器,缓冲电路会有更高的位移电流,而这会降低关闭过渡期间的ID和VDS交叠。

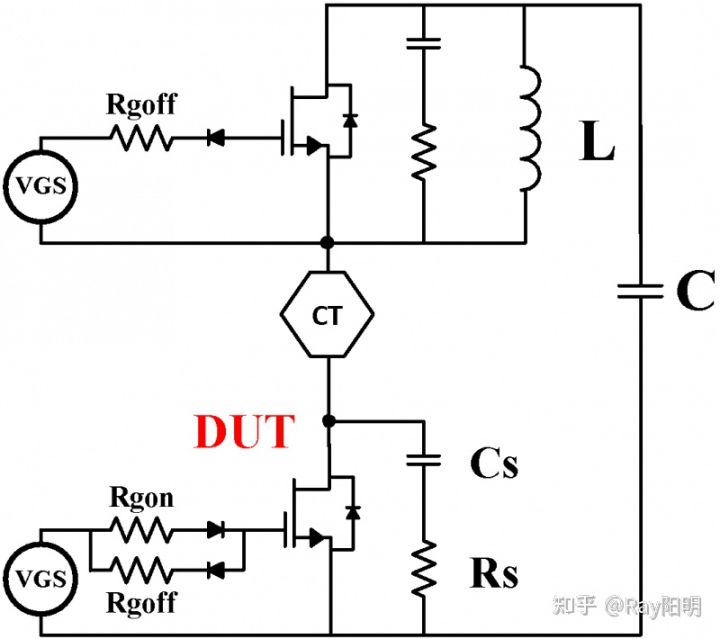

双脉冲测试(DPT)证实了RC缓冲电路的效果。它采用有电感负载的半桥配置。桥的高侧和低侧采用相同的器件,在低侧测量VGS、VDS和ID(图2)。电流变换器(CT)测量器件和缓冲电路电流。因此,测量的总开关损耗包含器件损耗和缓冲电路损耗。

我们都知道无论是功率半导体模块封装设计还是功率变换器的母线设计,工程师们都在力求杂散电感最小化,因为这样可以有效减小器件的开关振荡及过压风险,今天我们结合主流功率半导体厂商的SiC MOSFET模块,聊一下低杂感模块封装内部是如何设计的?

杂散电感

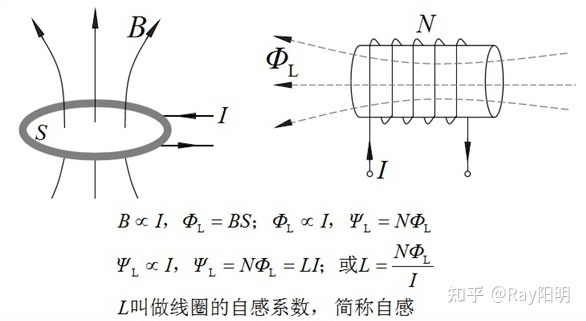

杂散电感是指由电路中的导体如:连接导线、元件引线、元件本体等呈现出来的等效电感 。电感是闭合回路的一种属性,是一个物理量。当线圈通过电流后,在线圈中形成磁场感应,感应磁场又会产生感应电势来抵制通过线圈中的电流变化,这种电流与线圈的相互作用关系称为电的感抗,也就是电感,以美国科学家约瑟夫·亨利命名。

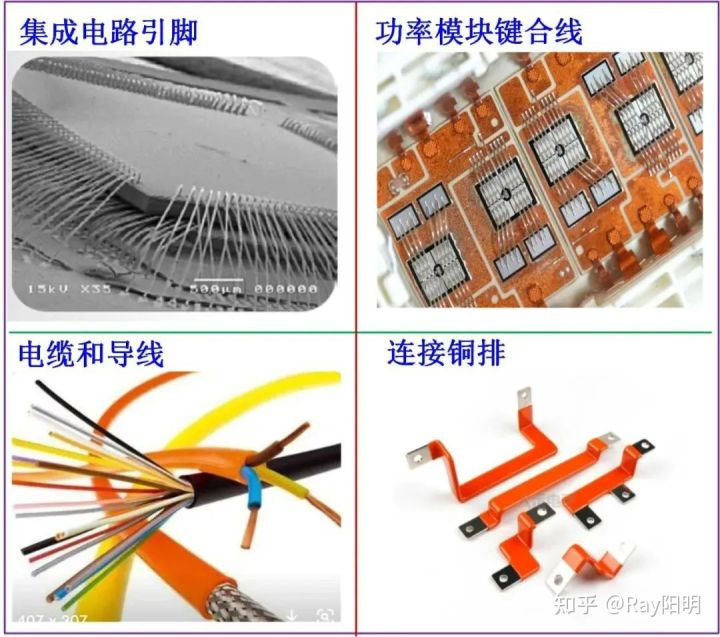

杂散电感产生影响的公式是Ls*di/dt,只有产生电流变化的路径,才会考虑其Ls。包含:

- 母线电容杂散电感;

- 母线电容到IGBT模块间的杂感;

- 模块内部杂散电感:包含端子间杂感、键合线及DCB覆铜层杂感等

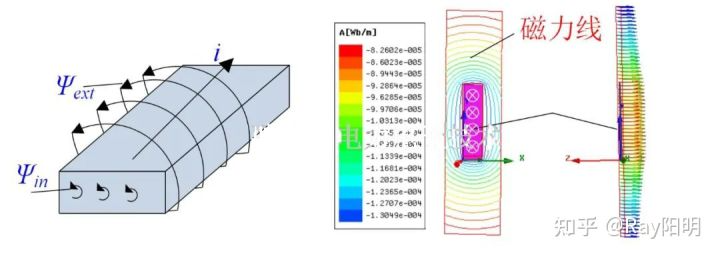

对于常规的电感比较好理解,也比较形象,以空心螺线管为例,线圈通入电流就会在线圈内部产生磁通。如果从能量角度理解:电感器是能够把电能转化为磁能而存储起来的元件,电感电流不能突变的本质原因是电流产生的磁场能不能突变。通常情况下,线圈的形状不变后,电感也不再变化,默认为常数,电感与磁场中的磁链关系如下图:

普通电感的感量一般是uH或mH级,而杂散电感是指这个电感不是故意设计出来的,是附加或寄生在导体上产生的,量级一般是nH级,任何一根导线无论它有多短都会存在寄生电感。

模块内部杂散电感

注:实际模块中的布局走线对Ls有很大影响,如果想要彻底搞清楚你所应用的模块杂散电感影响,建议做一次全方位换流路径的剖析

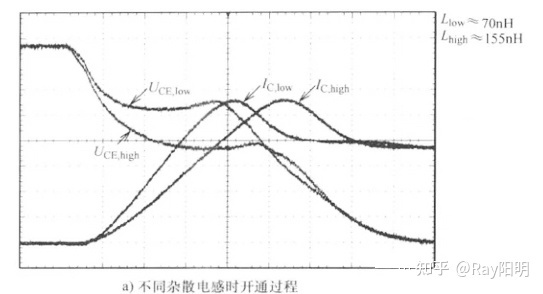

对开通影响:

- Ls越大,集电极-发射极电压Vce跌落越大,用双脉冲试验可观测其波形;

- Ls越大,集电极电流dic/dt越低;

- Ls越大,开通损耗Eon反而降低,由此可见,Ls对开通过程是有利的

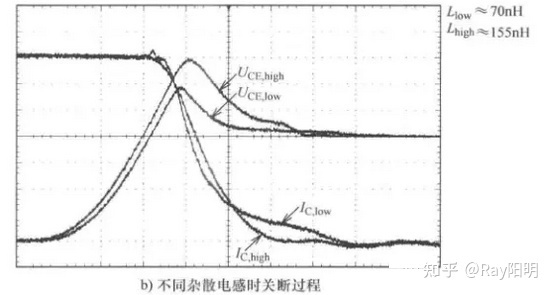

对关断的影响:

- Ls越大,集电极-发射极电压Vce电压过冲越大,过压击穿的风险越大;

- Ls越大,集电极电流ic下降的斜率越慢,到达拖尾区的时间越长,

- Ls越大,拖尾电流越不明显,关断越硬,关断损耗Eoff越大;

可见,Ls非常不利于关断

在前边分析反偏安全工作区RBSOA的时候知道,Ls对关断过程的影响极大地影响可用的母线电压Udc

即Vce=Udc+Lsdi/dt

关断过电压增加会引起IGBT内的电场扩展并移除更多载流子,剩余载流子构成拖尾电流;

如果杂散电感过大,高母线电压下,过高的电压尖峰导致拖尾电流降低甚至消失,产生强烈的关断震荡,即突然关断,对IGBT的FS层有重要影响

对于杂散电感理解虽不及螺线管形象,但电感与磁链的关系依然满足L=Ѱ/I。以矩形截面导体为例,杂散电感Lσ主要分为内电感Lin和外电感Lext。其中,内电感Lin由导体内部的磁链Ψin引起,大小随频率的增加而减小,主要是因为高频下由于集肤效应电流都走表面,导体内部没有电流,也就不存在磁链了;外电感Lext由导体外部的磁链Ψext引起,由导体结构决定,与频率无关,高频状态下,电感主要表现为外电感Lext。

杂感减小措施:

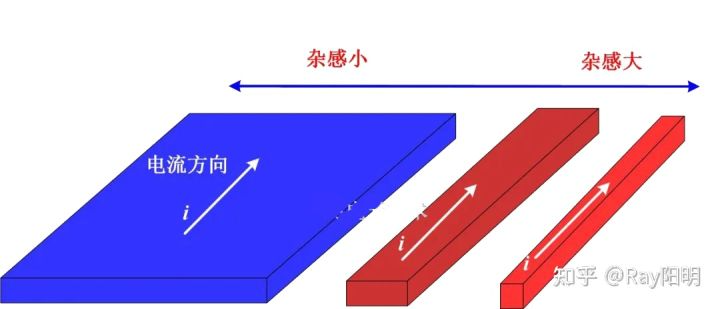

通过电感与磁链或磁通的关系,不难发现电感越大,单位电流产生的磁通量也就越多。反过来讲,如果单位电流产生的磁通量越少,那导体的电感也就与越小(这里是指不同形状的导体相比,对于一个导体,一旦形状固定,杂感基本就不会再变化了)。下面我们结合几种电流回路看一下导体形状和电流走向是如何影响杂感的。

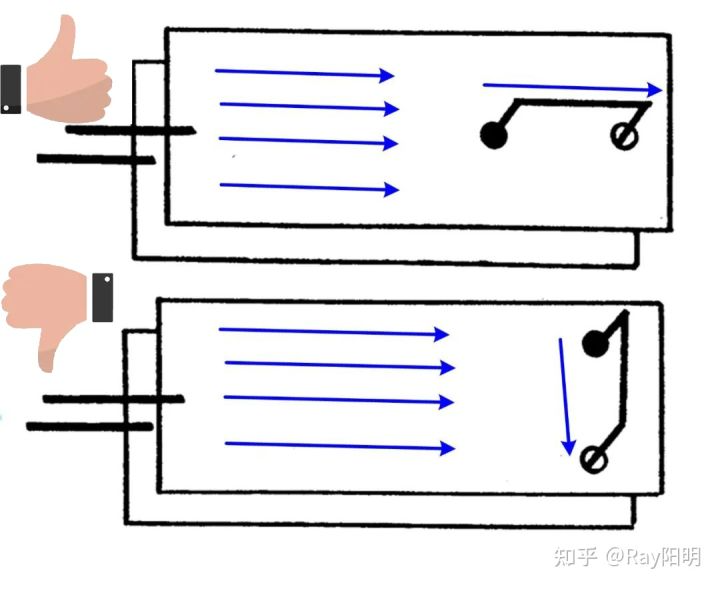

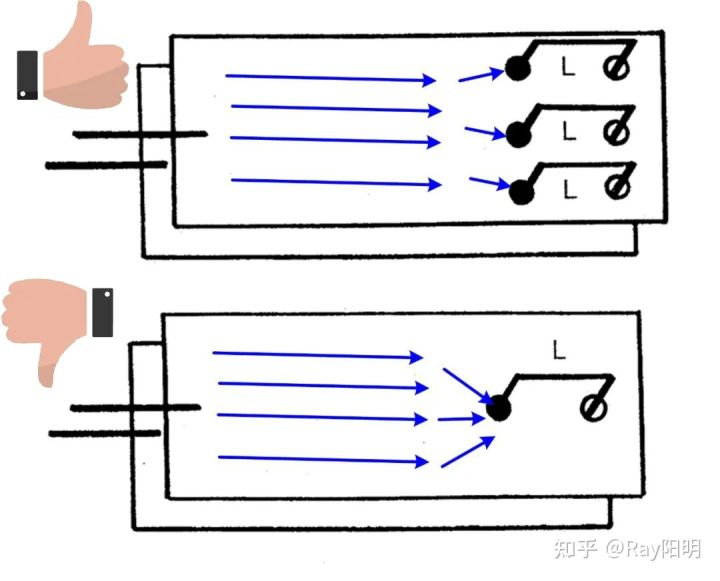

电路1:宽导体比窄导体杂感小,这个不难理解,可以把导体流过的电流想象成无数个并联的电流线,这样导体越宽,电流产生的磁通抵消也就越多,因此杂感也就越小。

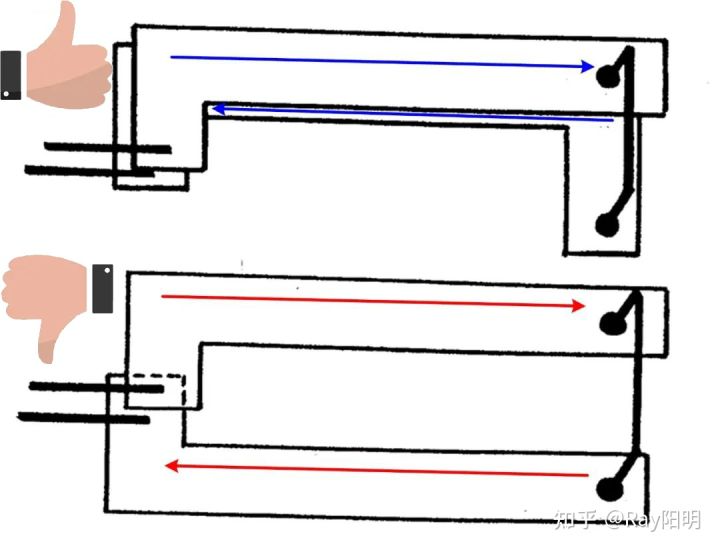

电路2:电流方向相反的两个叠层导体比平行导体杂感小,这个也很好理解,电流方向相反,上下电流产生的磁通就会抵消,因此杂感也就越小。

电路3:换流回路中的电流方向相反的数量越多,能够抵消的磁通越多,杂感也就越小。在这里可以把换流回路分段理解,电流相反的段数越多杂感也就越小。

电路4:导体互连并联点越多杂感也就越小,这里的互连点可以是电容并联,可以是功率器件并联,也可以是模块内部的芯片并联。

电路5:方向相反的电流距离越近,杂感也就越小。

通过上面分析可以看出,要想减小换流回路中的杂感,核心思路要么是把导线做宽,要么就是导线叠层,且距离越近越好,但本质思想是一样的都是磁场抵消。

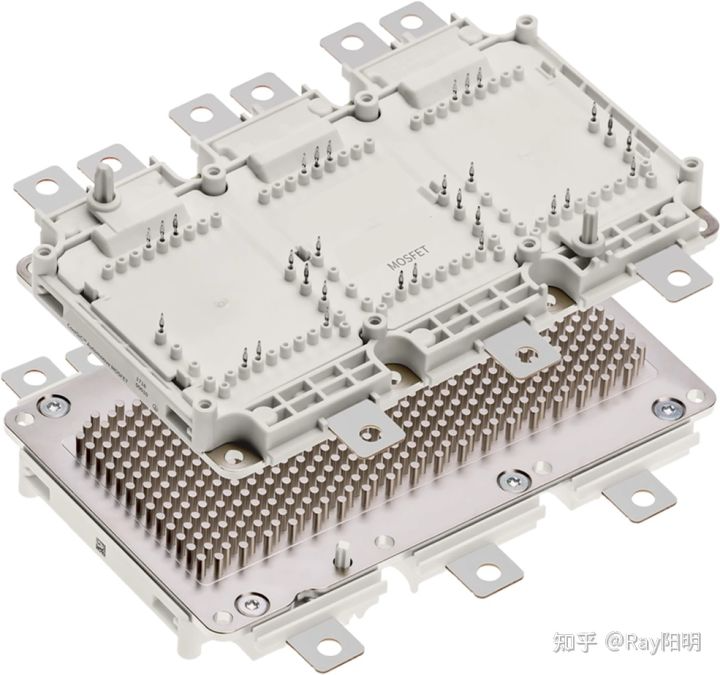

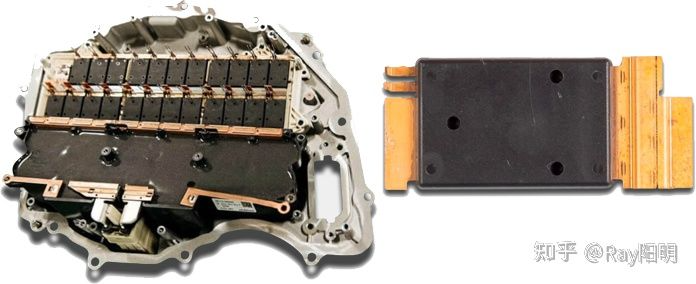

让我们来看看两大主流的Silicon Carbide MOS厂商Cree和Rohm模块内部是如何连接的:

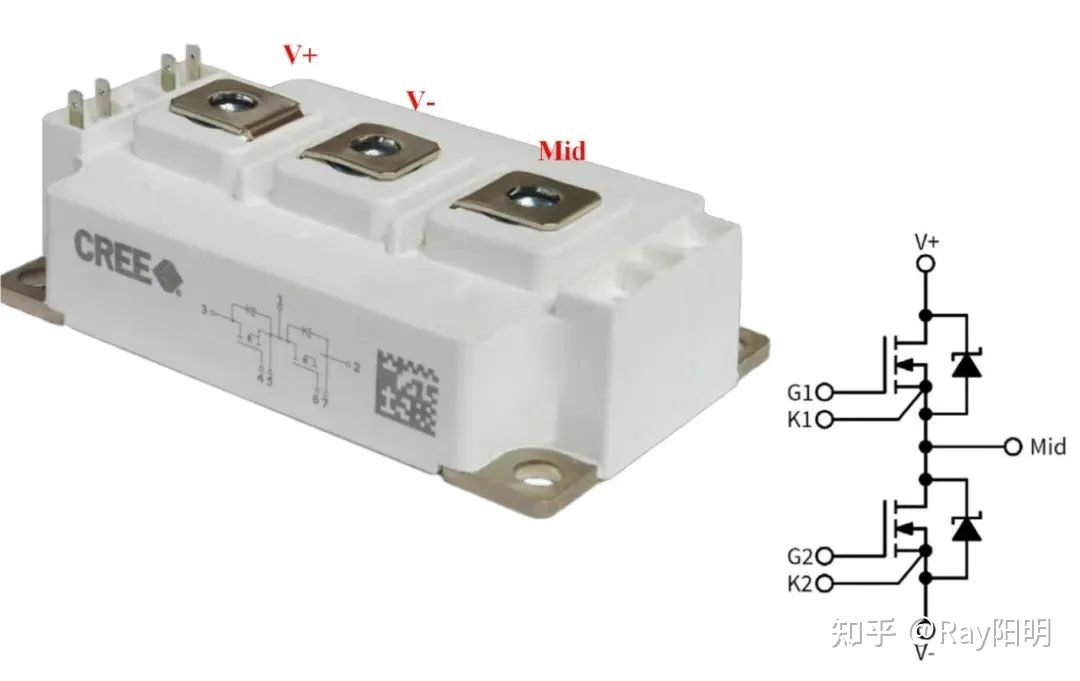

CREE

大功率SiC MOS 模块主要有三种封装,分别如下:

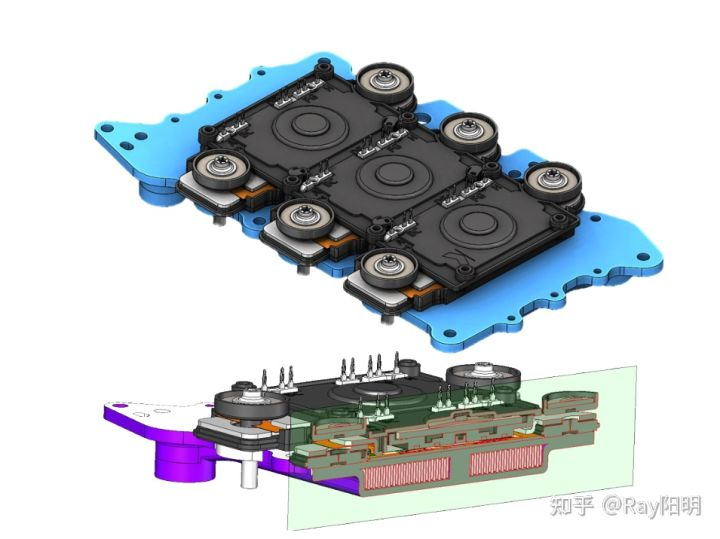

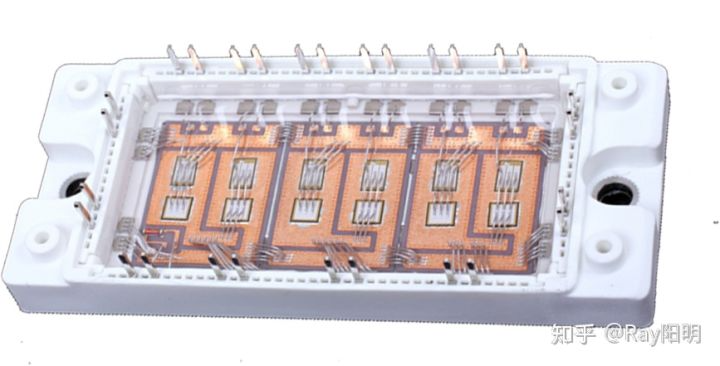

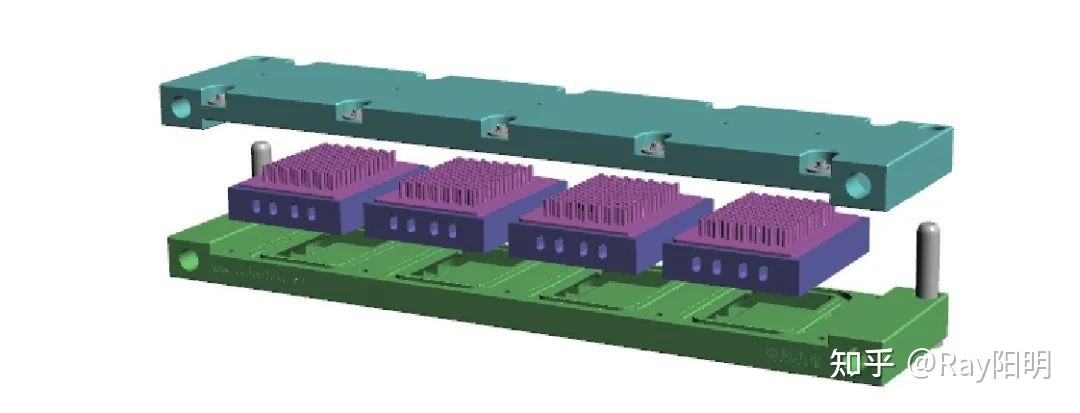

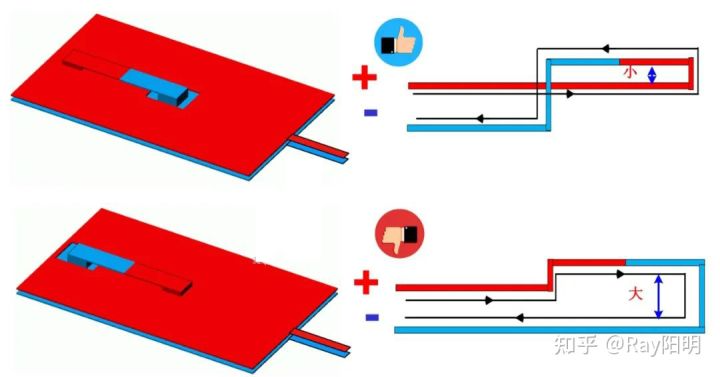

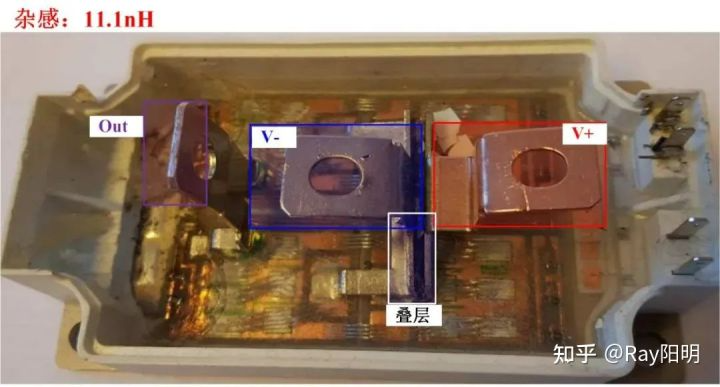

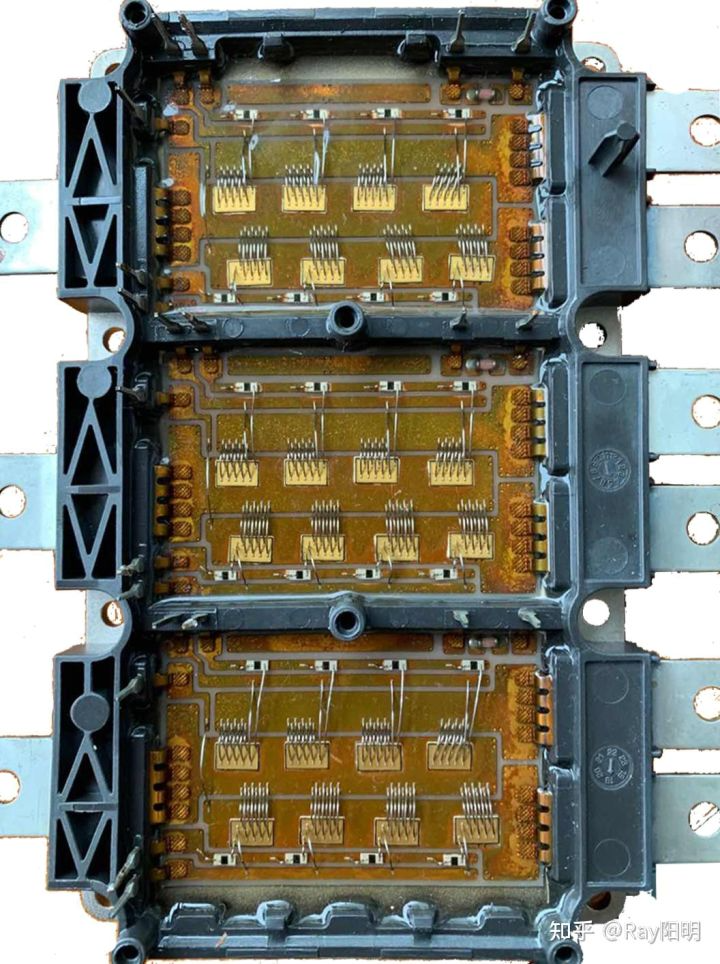

示例1:62 mm封装

下图为Cree 早期的62mm封装模块,这种封装目前在IGBT上还有大量应用。62mm模块的电压等级覆盖1200 V和1700V,1200V电压的模块电流从120A至530A,1700V模块只有225A一款,该模块封装内部的杂感为11.1nH。模块的内部结构如下图所示,正负连接铜排在模块内部采用叠层方式,因此在一定程度上减小了模块杂感。

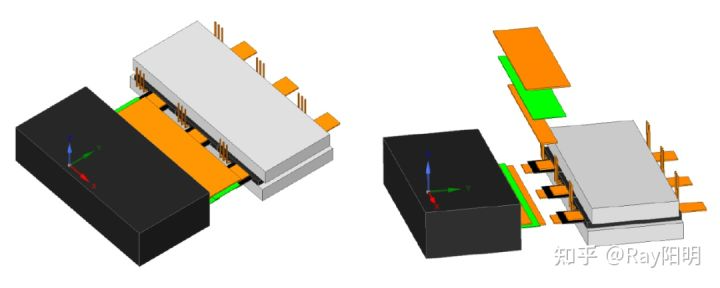

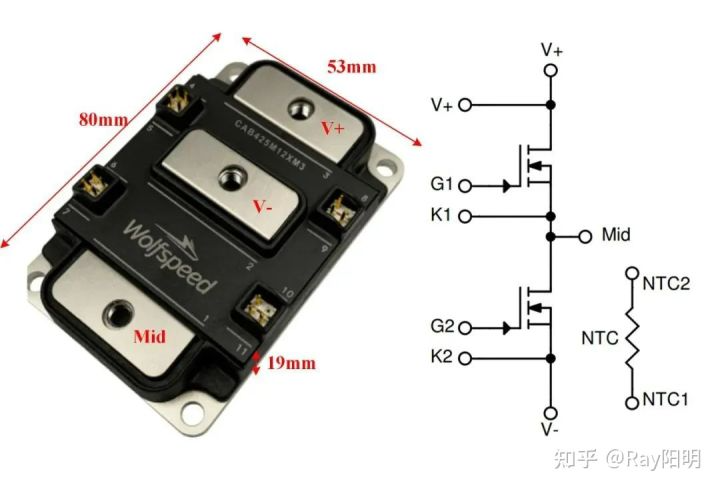

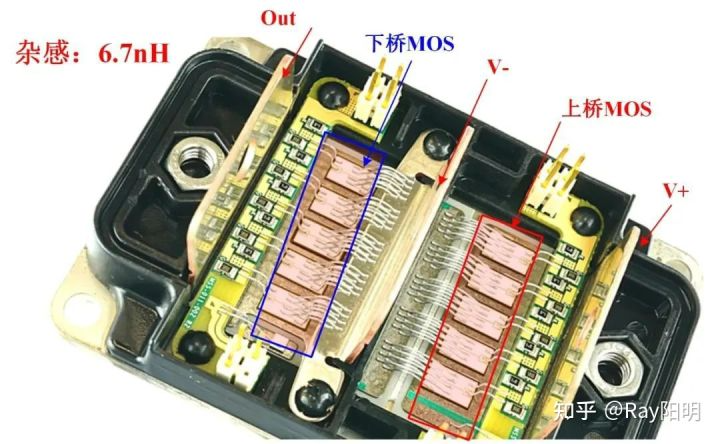

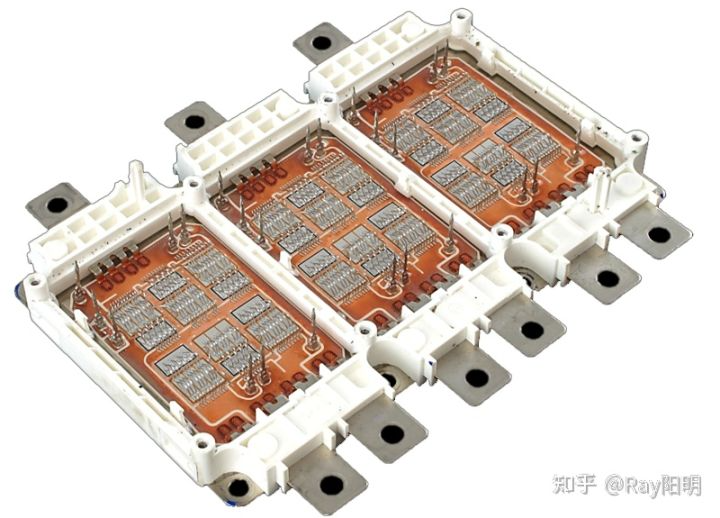

示例2:XM3 封装

XM3 封装电压等级为1200 V,电流等级覆盖 400A-450A,模块内部杂感为6.7nH。

模块的内部结构如下图,可以看出正负母线导体没有底层,但导体相对较宽,而且内部芯片并联,电流的方向都是平行并联的,非常顺,这样杂感也能降下来。

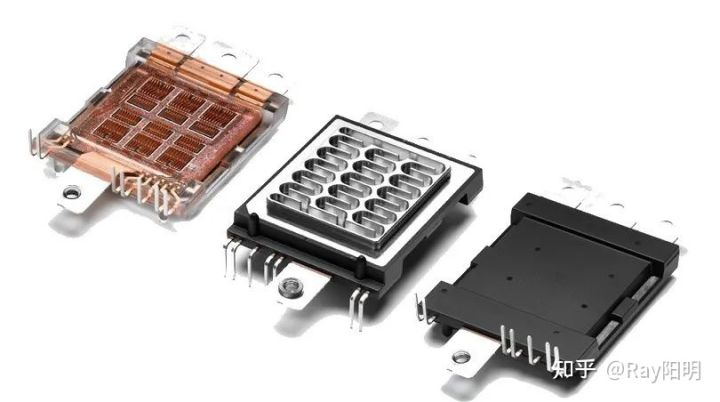

示例3:HM High Performance 62 mm封装

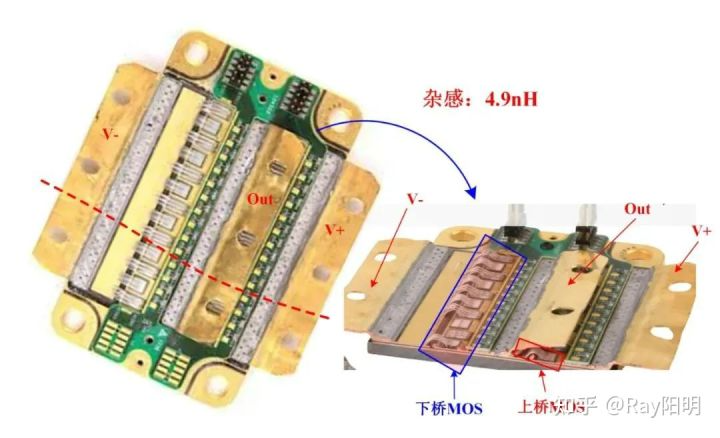

HM 62mm 封装的电压等级覆盖1200 V和1700V,1200V电压模块电流从480A至760A,1700V电压模块电流从380A至650A,模块内部的杂感在4.9nH。

模块的内部结构如下图,正负母线在两侧,且没有叠层,但正负母线比XM3封装更宽,这样可以进一步减小一部分杂感。

05

ROHM

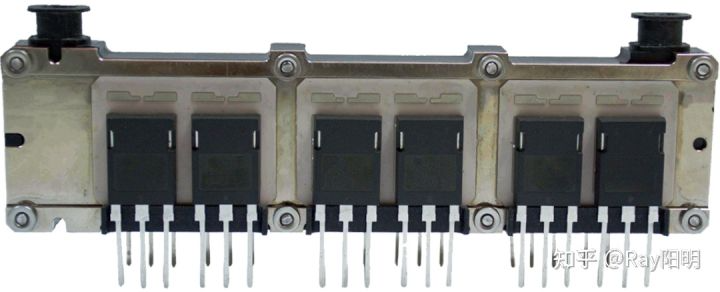

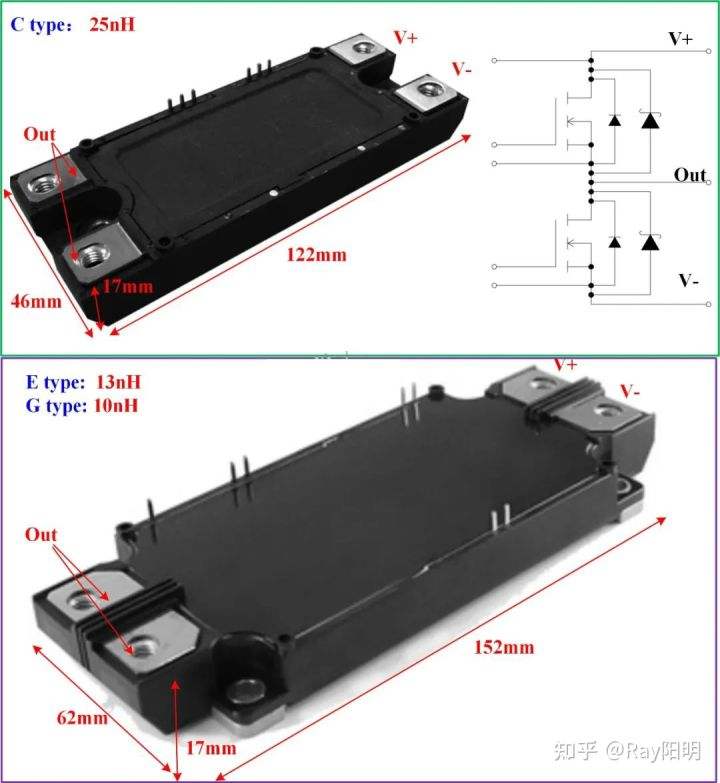

SiC模块电压等级覆盖1200V-1700V,主要有三种:C type、E type和 G type

模块外形尺寸如下图:

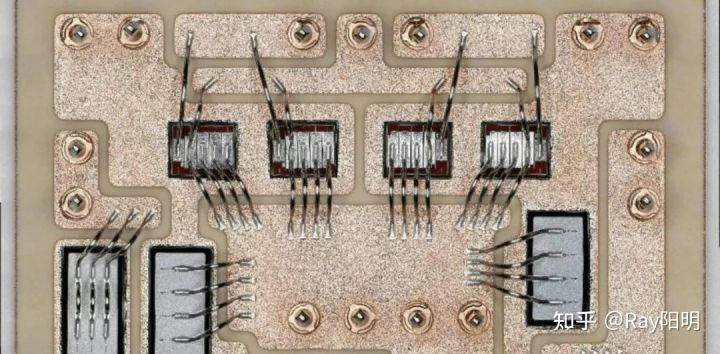

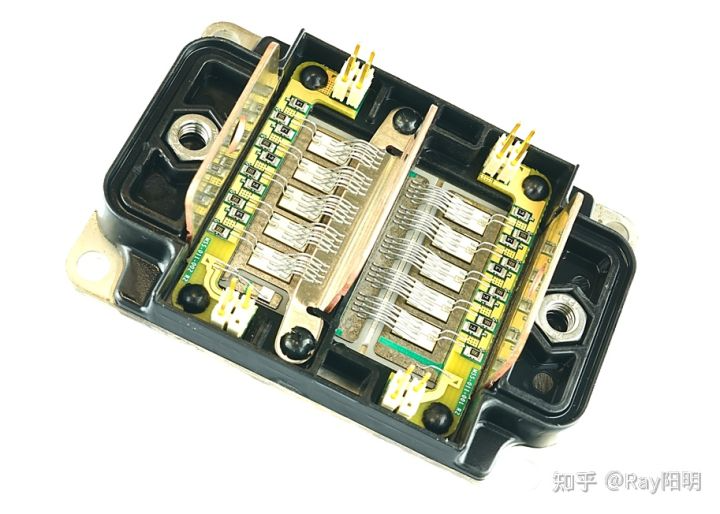

其中C type内部杂感为25nH,E type内部杂感为13nH,G type内部杂感为10nH。E type和G type模块外部尺寸一样,但G type封装模块的电流更大。C type模块的内部结构如下图:

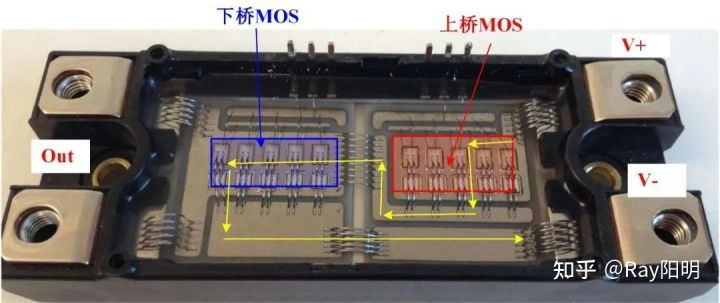

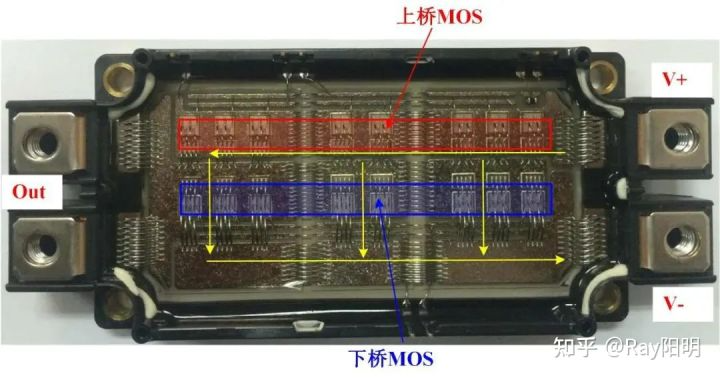

可以看出C type电流换流路径较长,而且上下桥MOS在两块独立的DCB上,因此杂感相对较大。E type模块的内部结构如下图:

可以看出E type封装比C type电流路径平行的段数变多了,因此杂感相比C type能够减小不少。G type封装老耿没有找到内部图片,猜测可能和E type差不多,只是内部并联的芯片数量会更多一些,因此电感相比E type会小一些。

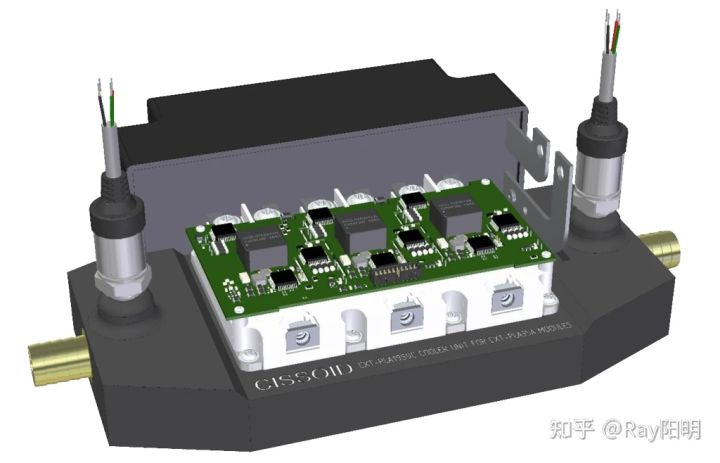

以下这家SiC模块,杂散电感号称

Module Stray Inductance(incl Terminals):2-3nH

猜猜是哪家的模块?评论区回复,加微信给出答案