一、填空题 16分(每空2分)

二、选择题 14分(每题2分)

三、大题7道 70分

第01章

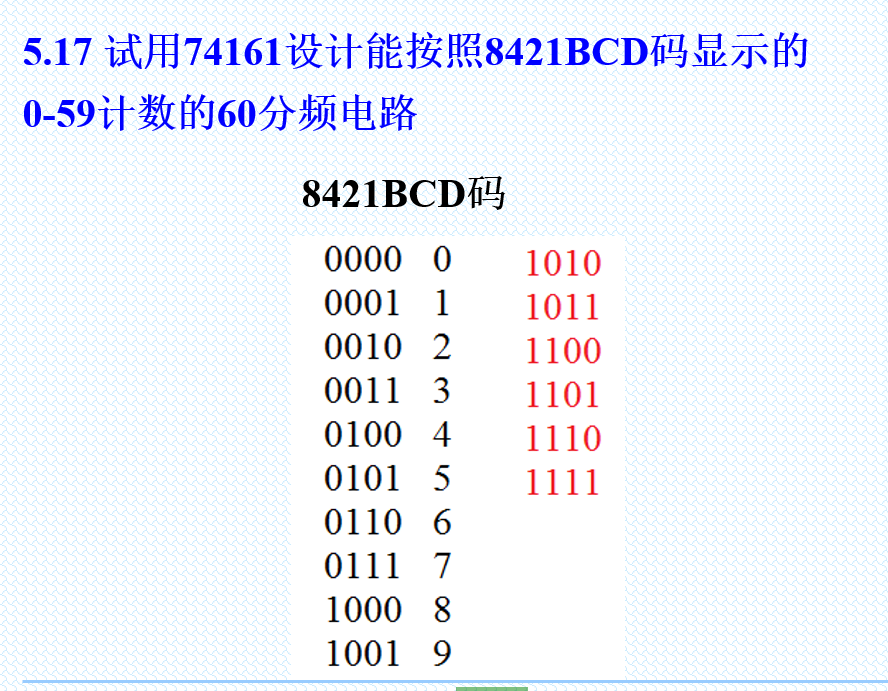

掌握二进制、八进制、十进制、十六进制间的互相转换,以及8421BCD码与各种进制之间的转换。

第02章

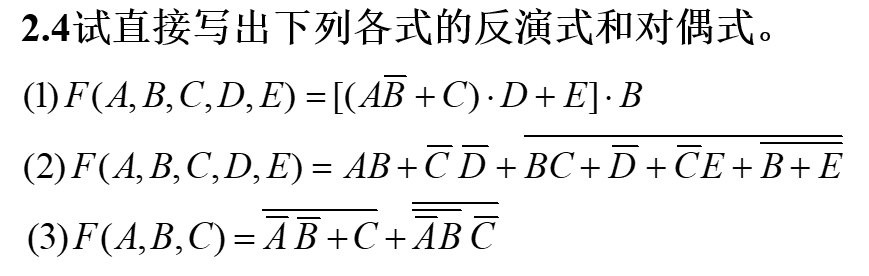

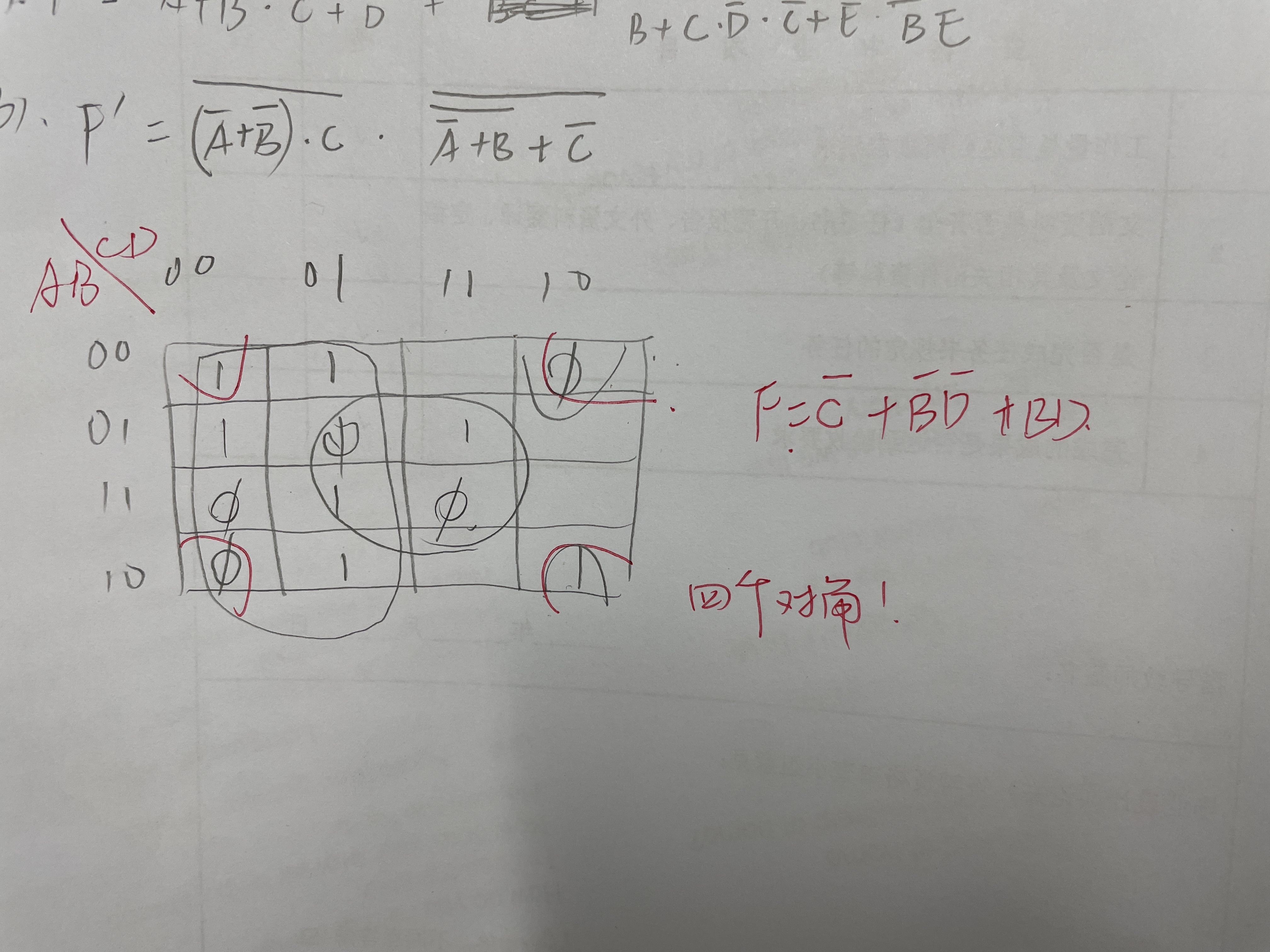

•熟悉最小项的主要性质。(相比18新增) •会写函数式的反演式和对偶式。

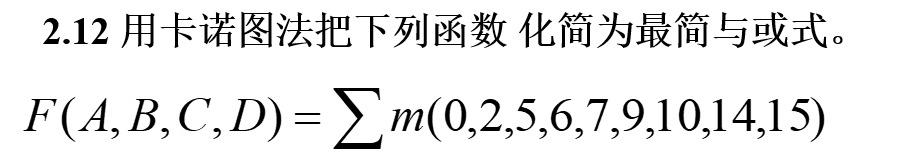

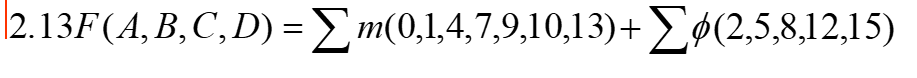

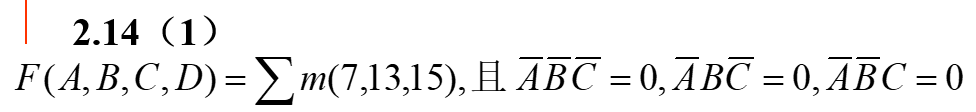

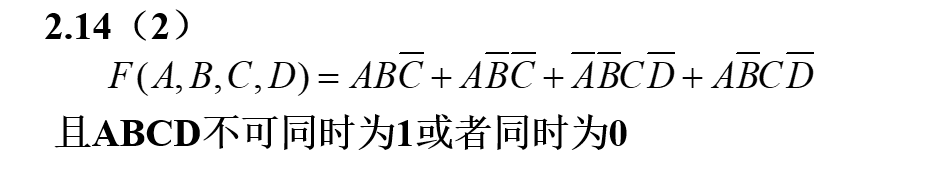

参考习题2.4 •重点掌握逻辑函数的卡诺图化简法。 参考书上例题、习题2.12~2.15 (相比18删去2.11)

第03章

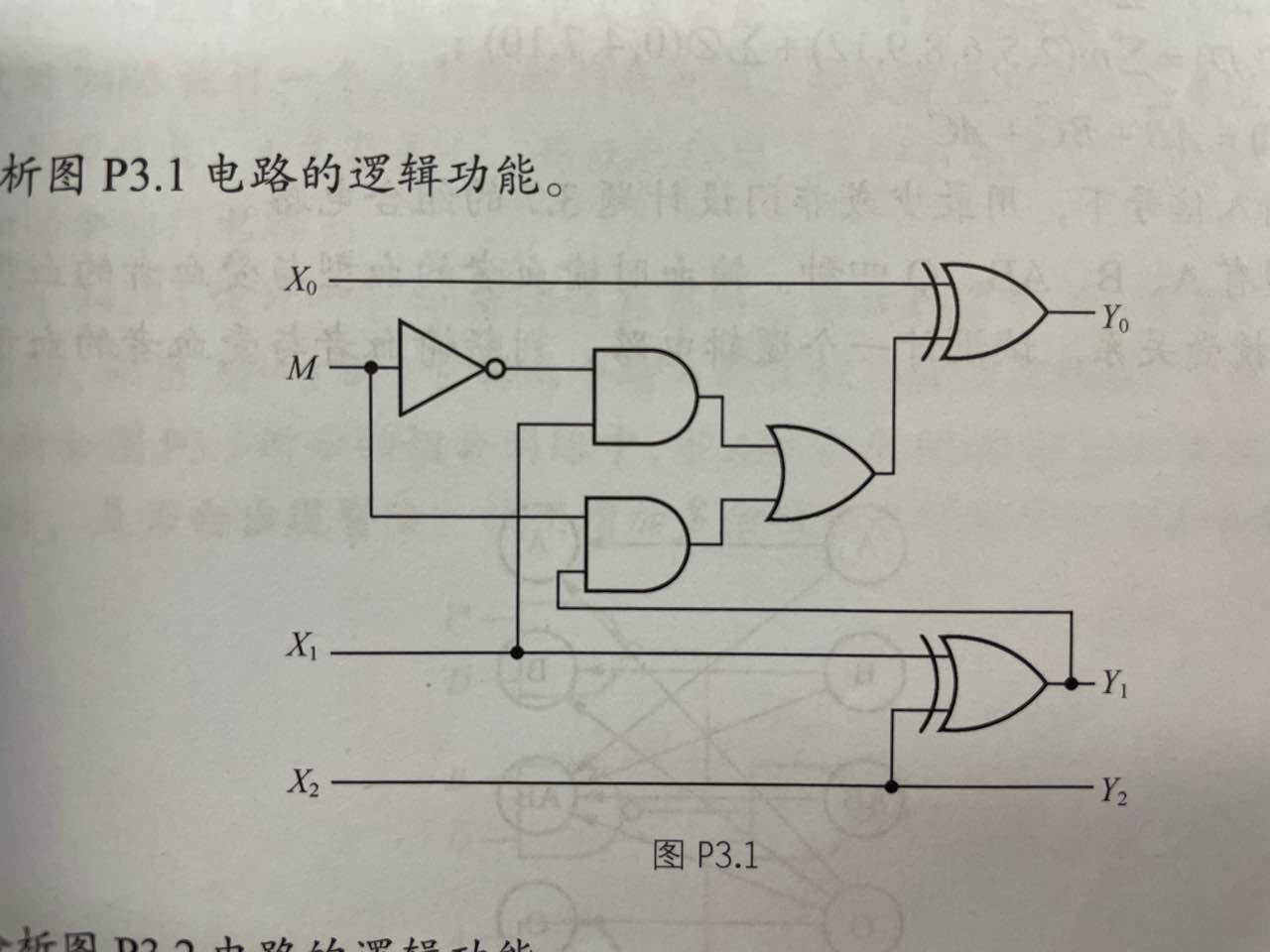

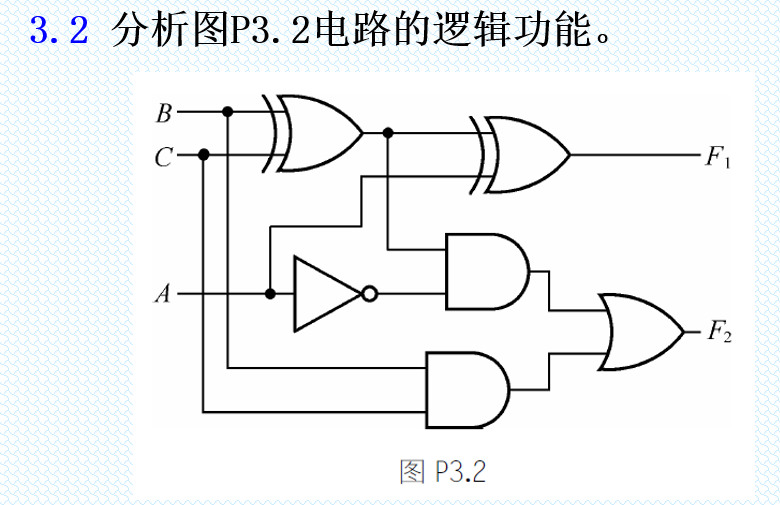

重点:MSI组合逻辑电路的应用(相比18删除SSI组合逻辑电路) (1) 小规模集成电路的分析与设计 书上例题、习题3.1 3.2**

3.1没做过,更重要是我不会做!

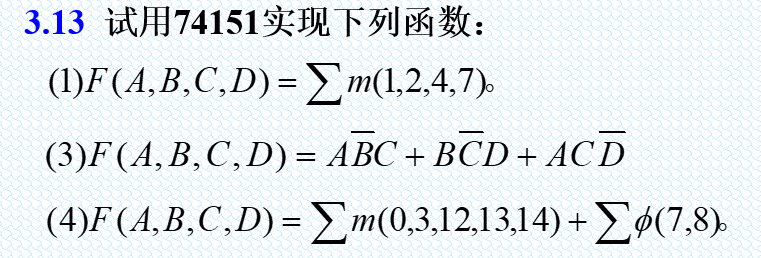

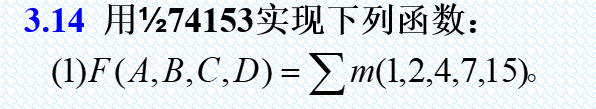

(2) 用数据选择器74151或74153设计任意逻辑函数

习题3.13 3.14

(3) 基于全加器74283和比较 器7485的简单设计

习题3.17 3.18 3.20

3.20没做过(老师上课说好像不用管这道题)

**(4) 以上涉及芯片的相关电路的分析

(删除74138设计)

第04章

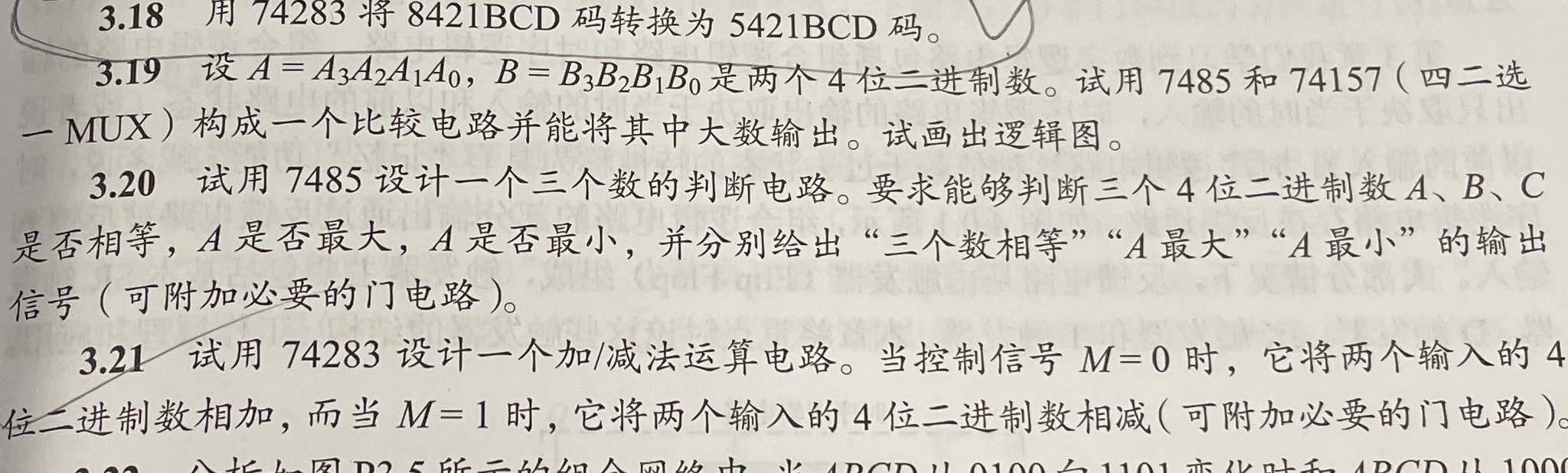

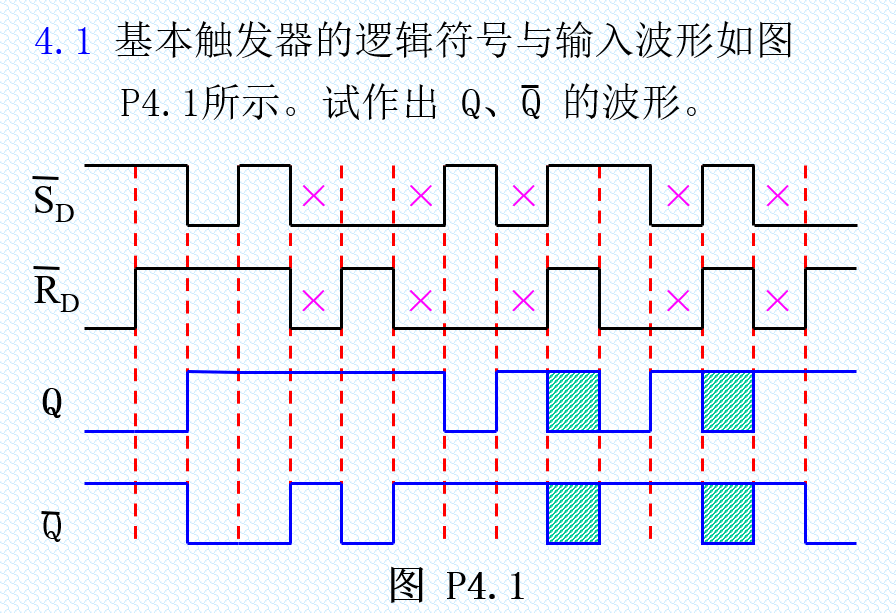

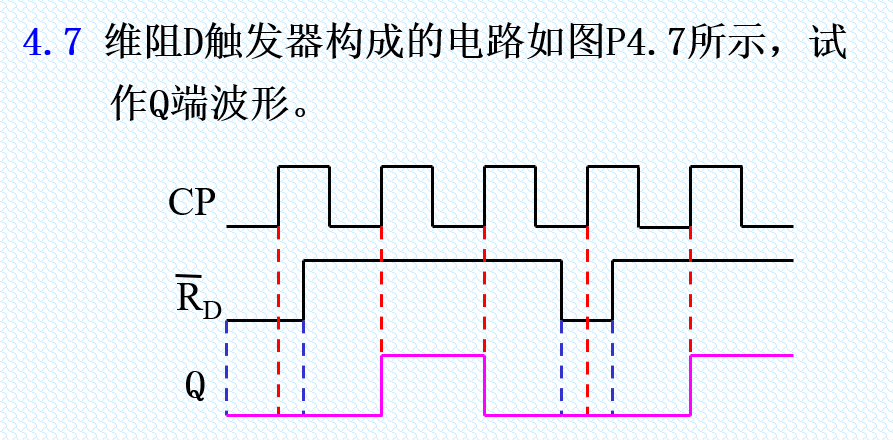

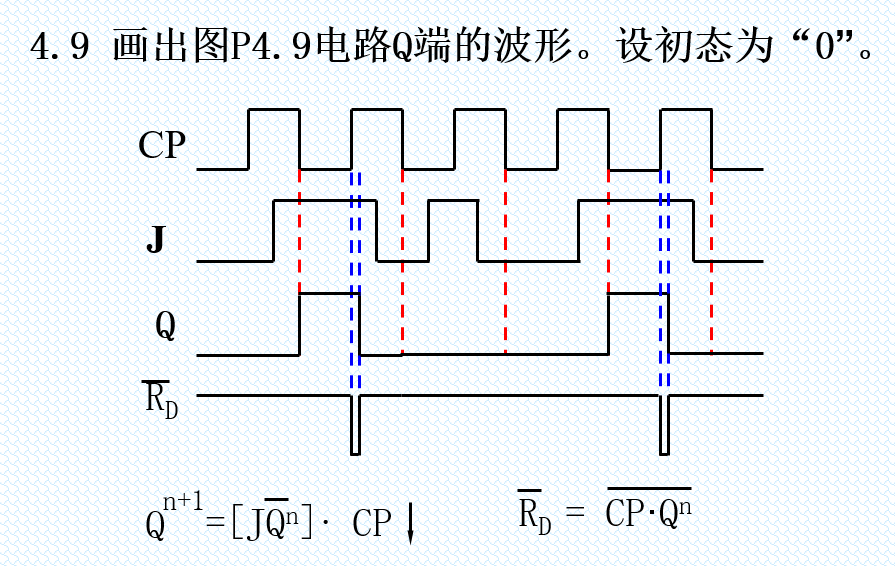

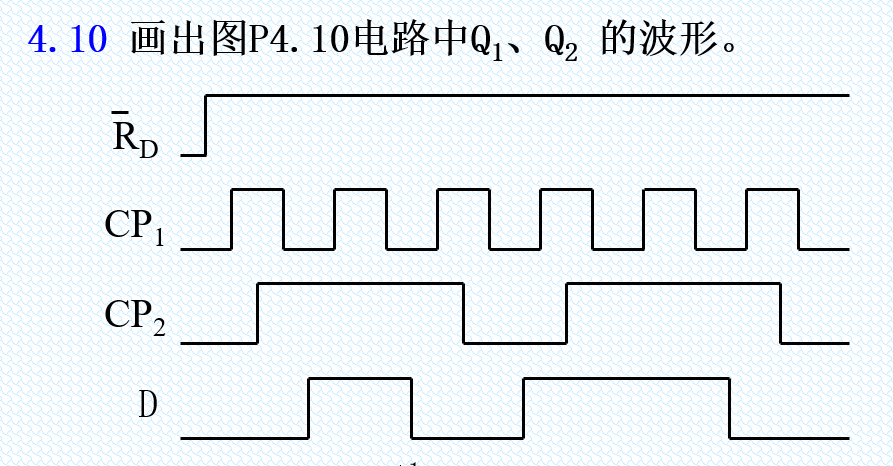

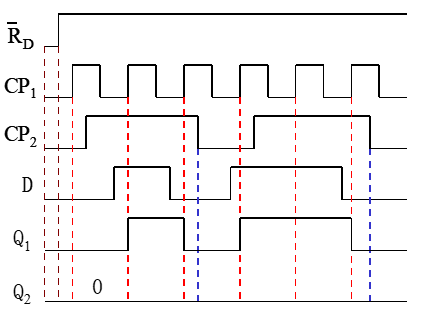

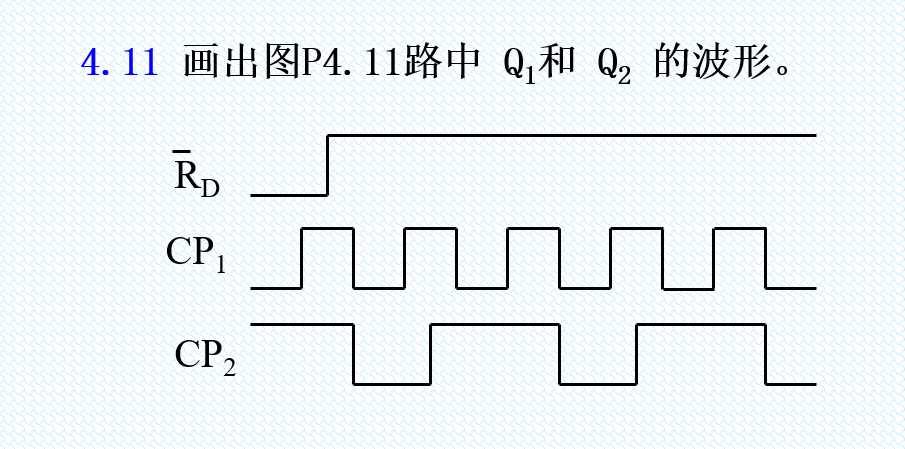

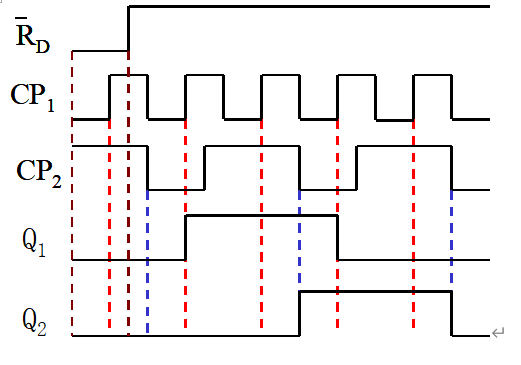

•画波形

掌握基于触发器的电路波形。

习题4.1、4.7、4.8、 4.9、 4.10, 4.11

(删除4.13 4.19,新增4.1 4.10 4.11)

老师说10、11多关注

注意JK是下降沿触发!!!

注意JK是下降沿触发!!!

第05章

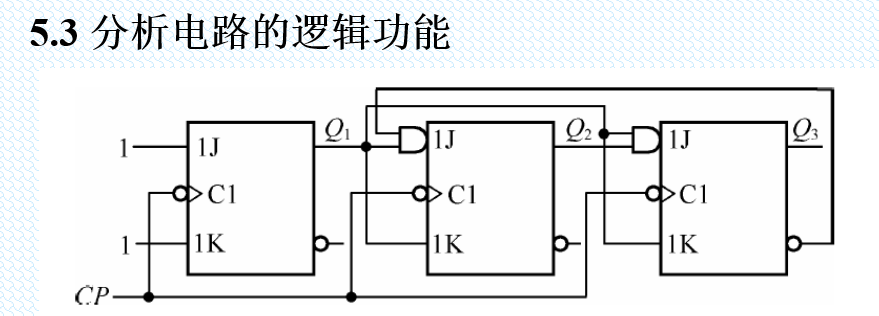

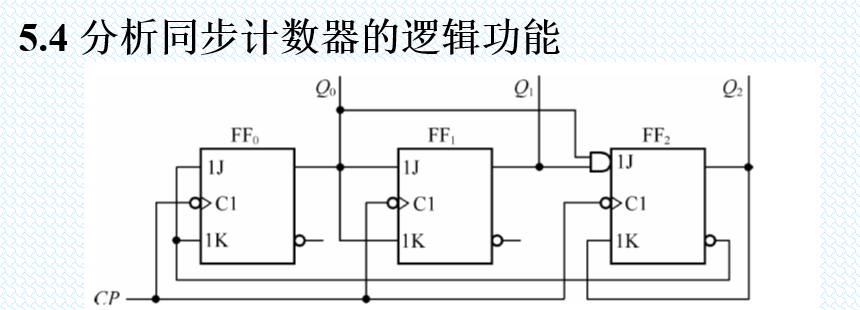

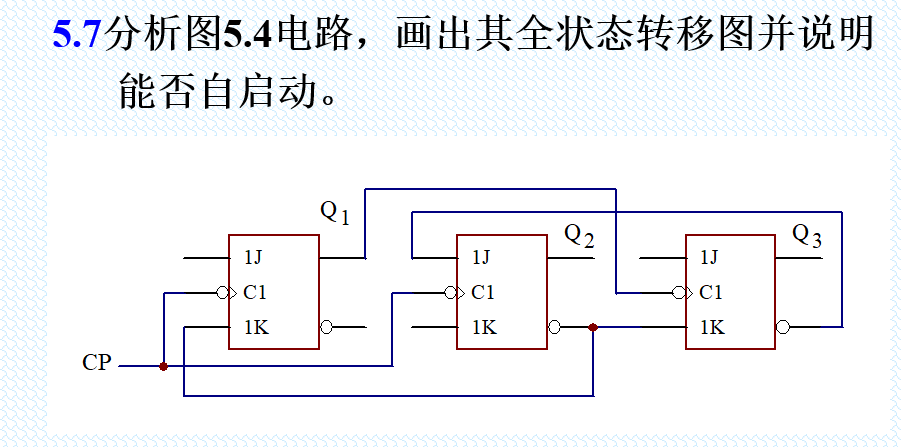

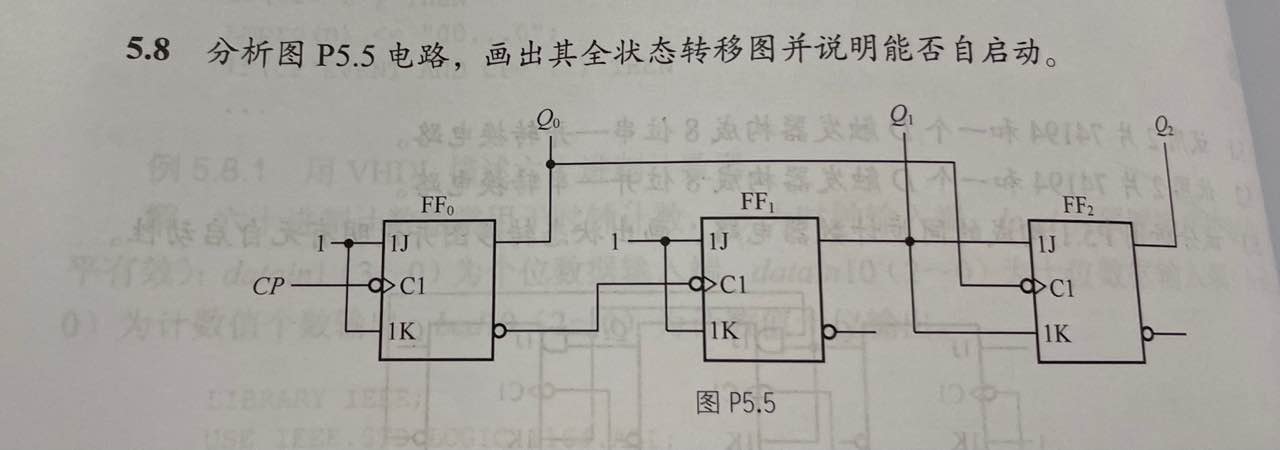

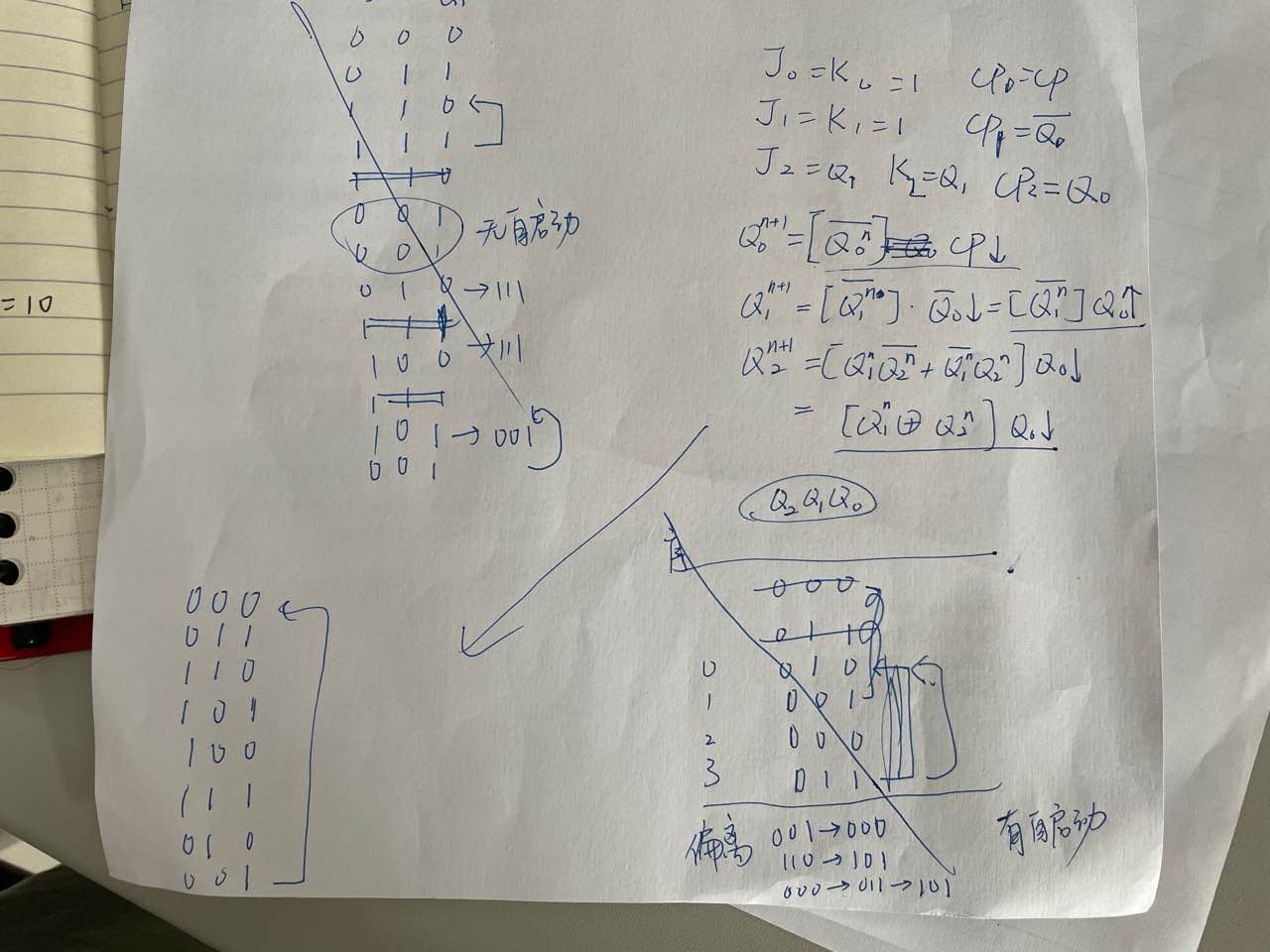

•SSI同步和异步时序电路的分析方法,会写激励方程、状态方程、会画状态转移表和状态转移图、会分析自启动性。 习题5.3、5.4、5.7、5.8

•相比2018删除例5.3.1、例5.3.2 例5.3.6、例5.3.7,删除波形图绘制的要求**

5.8没做过

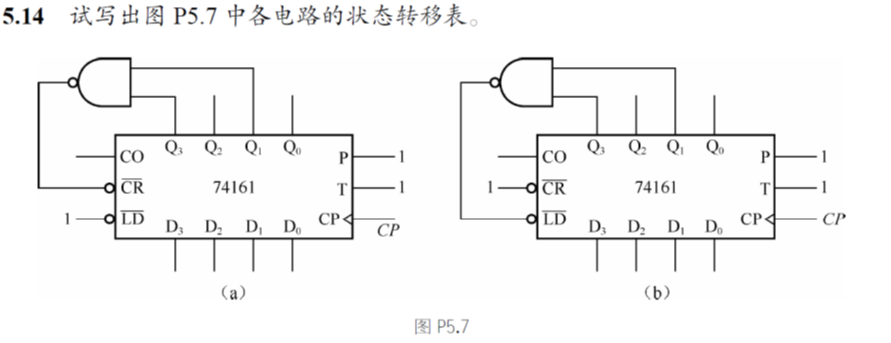

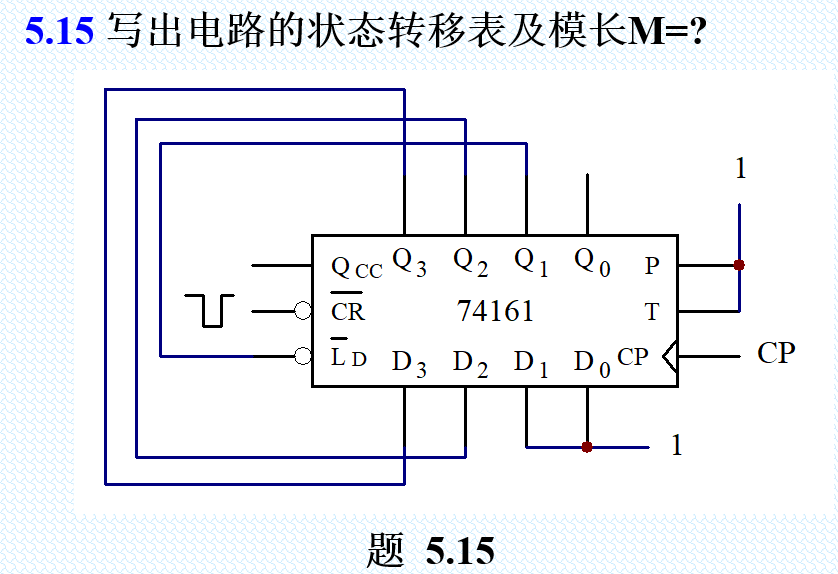

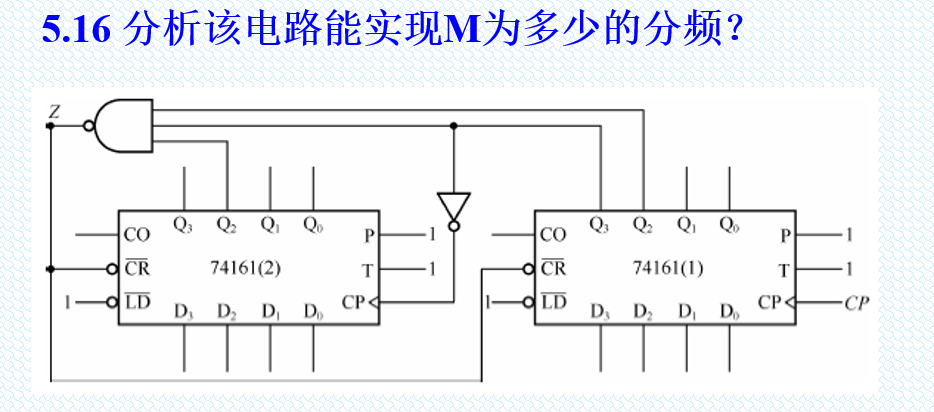

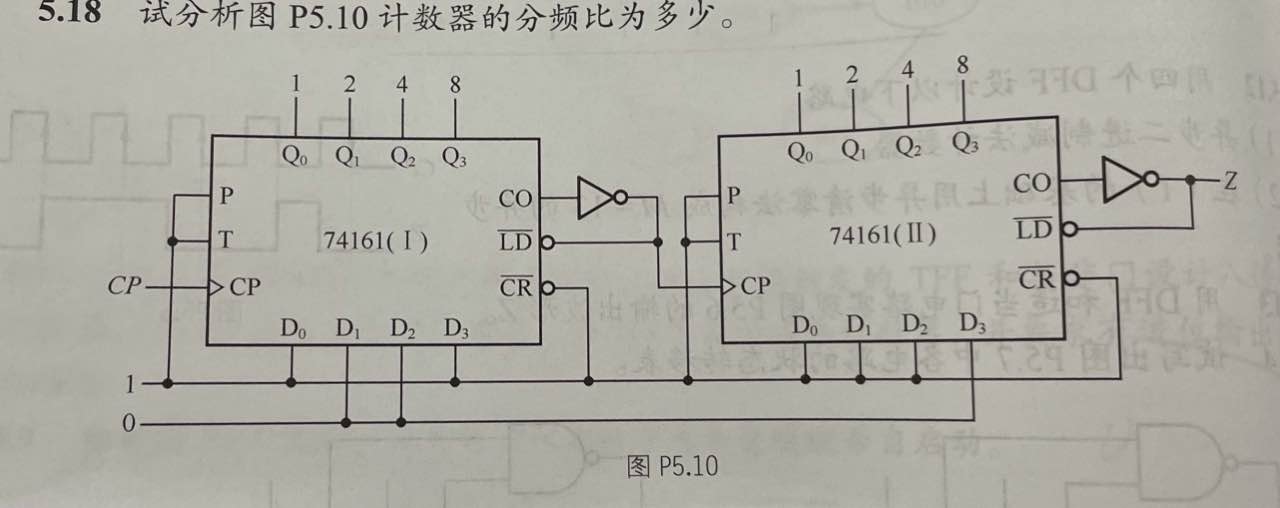

•基于MSI计数器74161的分析和设计

习题5.14 、5.15 、5.16 、5.17 、5.18 书上例题 •相比2018新增5.16 、5.17 、5.18 书上例题

5.18没做过

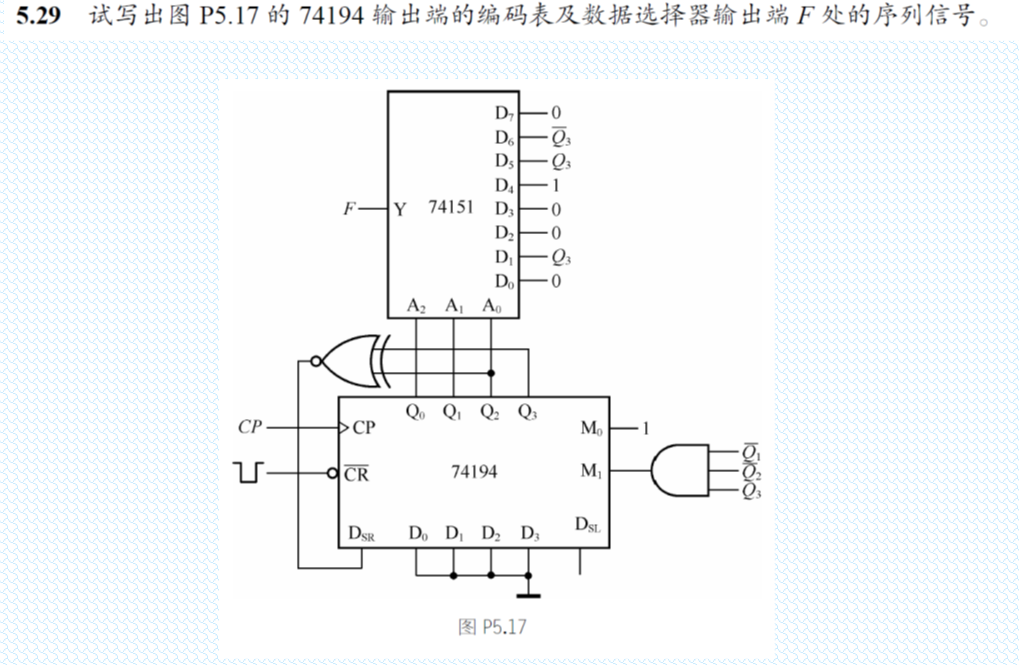

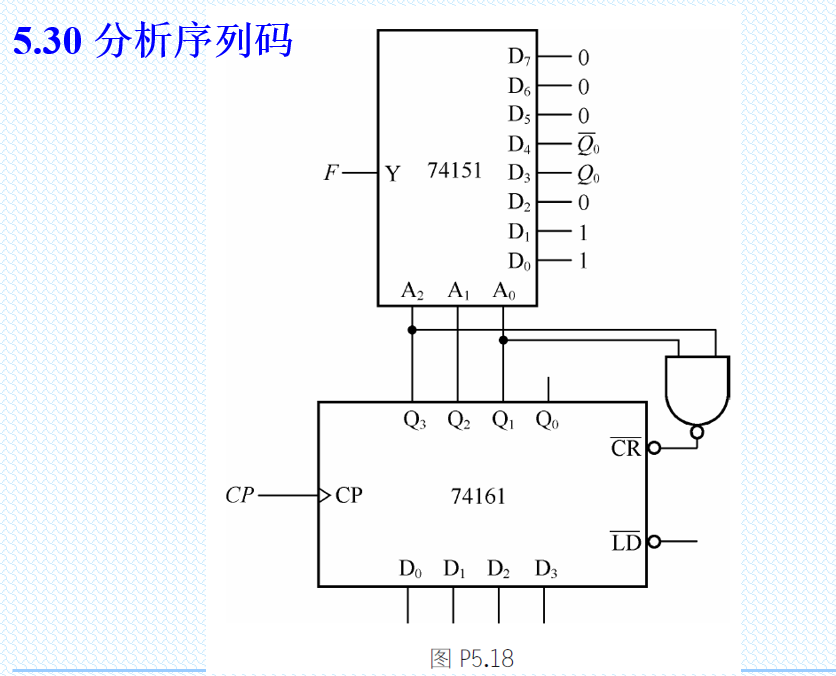

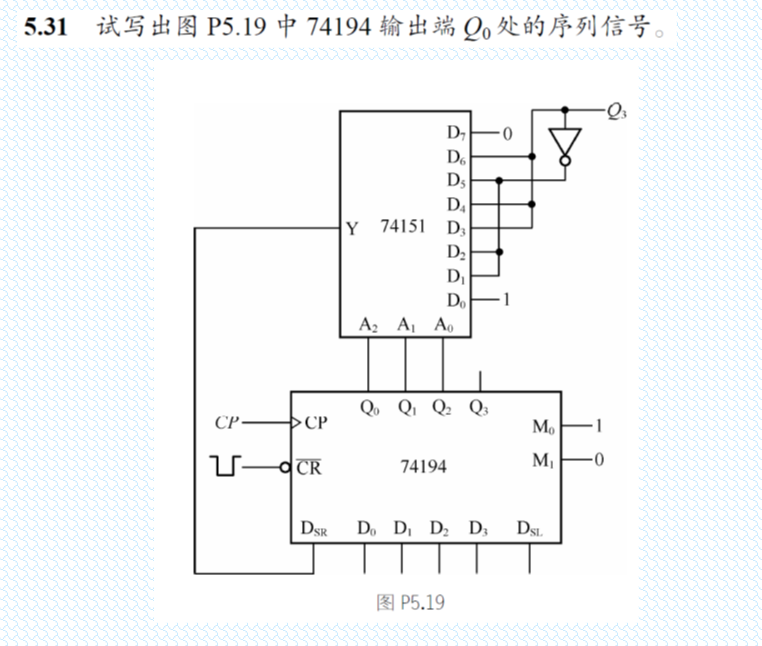

•序列信号发生器的分析和设计:

5.25(1) 5.29 5.30 5.31 例5.4.1, 例5.4.2

•相比2018新增5.25(1)例5.4.1, 例5.4.2

5.25(1)用DFF设计移位型序列信号发生器,要求产生11110000……

第06章

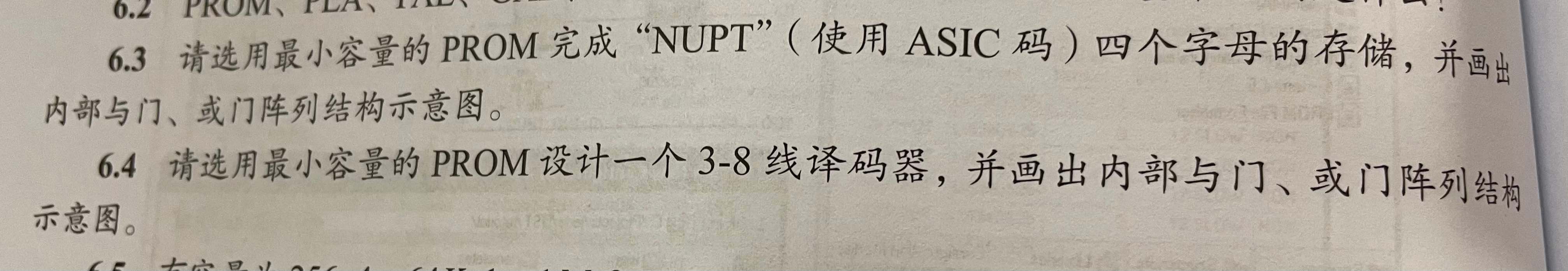

•利用PROM或PLA设计组合逻辑函数或设计特定功能的电路。

书上例题,习题6.3,6.4

相比2018新增PLA设计

第08章

•熟悉A/D变换和D/A变换的基本原理,不涉及大题,对应题型为填空或选择。

第8章AD和DA变换.ppt

Verilog HDL

•2021年考纲新增

Verilog+HDL.pptx

下降沿!!!!!!!!!

下降沿!!!!!!!!!