1 SelectIO资源简介

可配置的SelectIO驱动器和接收器广泛支持各种标准接口,强大的功能集包括可编程控制输出电压强度和压摆率,使用数字控制片内的阻抗匹配(DCI),以及内部产生参考电压(INTERNAL_VREF)的能力。

除了一些例外,每个I/O bank包含50个SelectIO引脚,每个存储区末尾的2个特殊引脚只能用于单端I/O标准,剩下的48个引脚可以使用两个SelectIO引脚与单端或差分标准配合使用,组合在一起作为正/负(P/N)对。每个SelectIO资源都包含输入、输出和三态驱动器。

SelectIO引脚可配置为各种I/O标准,包括单端和差分:

- 单端I/O标准:例如,LVCMOS、LVTTL、HSTL、PCI和SSTL;

- 差分I/O标准:例如,LVDS、Mini_LVDS、RSDS、PPDS、BLVDS和

差分HSTL和SSTL。

单端和常规IOB基本上是等效的,除了单端IOB没有连接产生输出差分信号的资源。在大多数器件中,单端IOB是位于每个I/O bank末端的两个引脚,每个I/O bank中的其他48个引脚的常规IOB可以实现单端和差分I/O标准。每个IOB都直接连接含有ILOGIC/OLOGIC对的逻辑资源,用于数据的输入输出和IOB的三态控制,ILOGIC和OLOGIC可以分别配置为ISERDES和OSERDES。

2 通用标准原语列表

Xilinx软件库包含大量原语列表,可支持各种原语。

单端I/O标准原语:

| 原语 | 说明 |

|---|---|

IBUF |

输入缓冲器 |

IBUF_IBUFDISABLE |

具有缓冲器禁用控制的输入缓冲器 |

IBUF_INTERMDISABLE |

具有缓冲器禁用和IN_TERM禁用控制的输入缓冲器 |

IBUFG |

时钟输入缓冲器 |

IOBUF |

双向缓冲器 |

IOBUF_DCIEN |

具有DCI禁用和缓冲器禁用控制的双向缓冲器 |

IOBUF_INTERMDISABLE |

具有IN_TERM禁用和缓冲器禁用控制的双向缓冲器 |

OBUF |

输出缓冲器 |

OBUFT |

三态输出缓冲器 |

差分I/O标准原语:

| 原语 | 说明 |

|---|---|

IBUFDS |

差分输入缓冲器 |

IBUFDS_DIFF_OUT |

具有差分输出的差分输入缓冲器 |

IBUFDS_DIFF_OUT_IBUFDISABLE |

具有差分输出和缓冲器禁用控制的差分输入缓冲器 |

IBUFDS_DIFF_OUT_INTERMDISABLE |

具有差分输出、缓冲器禁用和IN_TERM禁用控制的差分输入缓冲器 |

IBUFDS_IBUFDISABLE |

具有缓冲器禁用控制的差分输入缓冲器 |

IBUFDS_INTERMDISABLE |

具有缓冲器禁用和IN_TERM禁用控制的差分输入缓冲器 |

IBUFGDS |

差分时钟输入缓冲器 |

IBUFGDS_DIFF_OUT |

具有差分输出的差分时钟输入缓冲器 |

IOBUFDS |

差分双向缓冲器 |

IOBUFDS_DCIEN |

具有DCI禁用和缓冲器禁用控制的差分双向缓冲器 |

IOBUFDS_DIFF_OUT |

具有来自输入缓冲器差分输出的差分双向缓冲器 |

IOBUFDS_DIFF_OUT_DCIEN |

具有来自输入缓冲器差分输出、DCI禁用和缓冲器禁用控制的差分双向缓冲器 |

IOBUFDS_DIFF_OUT_INTERMDISABLE |

具有来自输入缓冲器差分输出、IN_TERM禁用和缓冲器禁用控制的差分双向缓冲器 |

IOBUFDS_INTERMDISABLE |

具有缓冲器禁用和IN_TERM禁用控制的差分双向缓冲器 |

OBUFDS |

差分输出缓冲器 |

OBUFTDS |

差分三态输出缓冲器 |

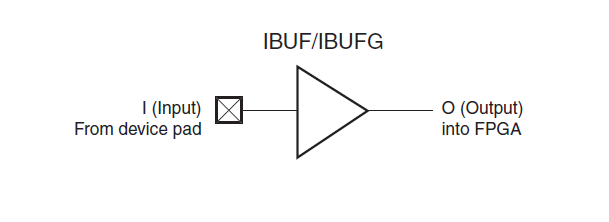

IBUF 与 IBUFG

用作器件输入的信号必须使用输入缓冲器(IBUF)。

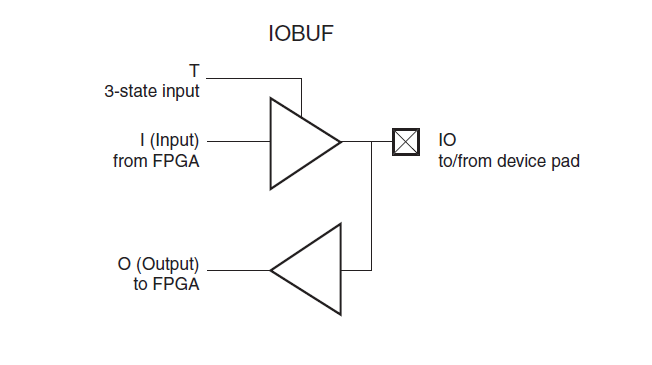

IOBUF

当双向信号需要输入缓冲器和具有高阻控制的3态输出缓冲器时,需要使用IOBUF原语。

T引脚设置为逻辑高电平将禁用输出缓冲器。

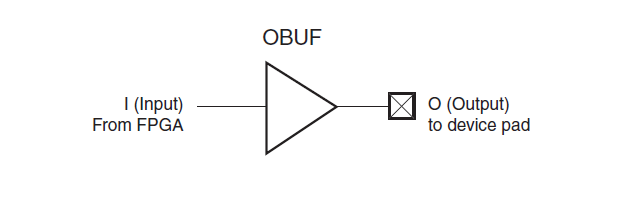

OBUF

必须使用输出缓冲器(OBUF)将器件的信号驱动到外部输出引脚。

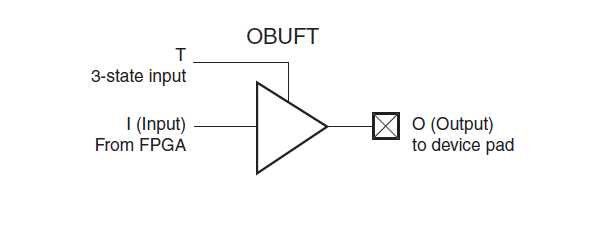

OBUFT

通用3态输出缓冲器OBUFT原语通常实现3态输出或双向I/O。

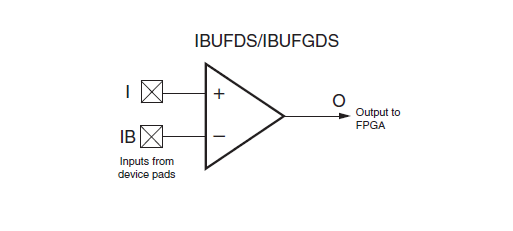

IBUFDS 与 IBUFGDS

对于差分原语的用法和规则类似于单端SelectIO原语,差分SelectIO原语在器件上有两个引脚,用于差分对中的P和N通道引脚,N通道引脚具有B后缀。IBUFDS和IBUFGDS原语相同,当差分输入缓冲器用作时钟输入时使用IBUFGDS。

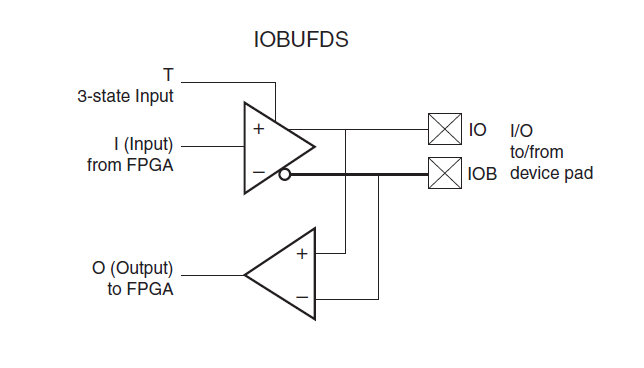

IOBUFDS

差分输入/输出缓冲原语。

T引脚设置为逻辑高电平将禁用输出缓冲器。

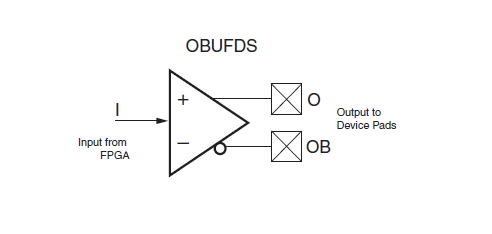

OBUFDS

差分输出缓冲原语。

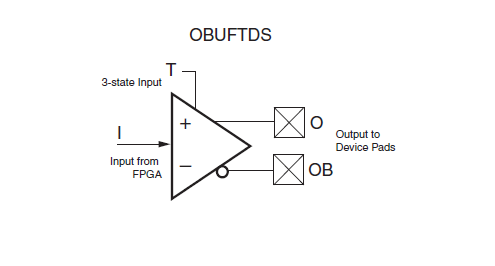

OBUFTDS

差分3态输出缓冲原语。

3 SelectIO逻辑资源

Xilinx FPGA的基本I/O逻辑资源包括以下内容:

- 组合输入/输出;

- 三态输出控制;

- 寄存器输入/输出;

- 寄存器三态输出控制;

- 双倍数据速率(DDR)输入/输出;

- DDR三态输出控制;

- IDELAY为用户控制提供可调节、精分辨率的延迟抽头;

- ODELAY为用户控制提供可调节、精分辨率的延迟抽头;

- SAME_EDGE输出DDR模式;

- SAME_EDGE和SAME_EDGE_PIPELINED输入DDR模式。