第1章 FPGA发展与展望

1.1 电子管到集成电路

1904年,英国物理学家约翰•弗莱明(John Fleming)发明了世界上第一个电子管;

1947年,美国贝尔实验室的威廉•肖克利(Shockley William Bradford)和他的同事约翰•巴丁(John Bardeen)、沃尔特•布拉德(Walter Brattain)发明了世界上第一个晶体管;

1958年美国德州仪器公司杰克•基尔比(Jake Kilby)发明了集成电路;

2008年,Intel公司发布酷睿 i7 CPU;

现今,超大规模集成电路ASIC和FPGA。

1.2 可编程逻辑器件

首先使用的是一种基于ROM的组合逻辑(ROM-Based Combinational Logic)。1978年,MMI(Monolithic Memories Inc)的约翰•博肯(John Birkner)和H•T•Chua发明了第一个可编程逻辑阵列PLA(Programmed Logic Array)。

1.3 PLA工作原理

由于任何组合逻辑都可以描述成逻辑函数的SOP乘积项(积之和,Sum of Product),理论上就可以用可编程的与或阵列进行实现。

1.4 复杂通用逻辑阵列

莱迪思推出称之为复杂通用逻辑阵列CPLD(Complex Programmable Logic Device)的器件。CPLD已经具有可编程逻辑宏单元MC、复杂的I/O单元互连、全铜层等长连接线和电路延迟时间预知。

1.5 现场可编程逻辑阵列FPGA

FPGA即现场可编程逻辑阵列(Field-Programmable Gate Array)具有几乎完美的现场编程架构,成为新一代电子硬件设计的平台。

FPGA通过查找表(LUT)实现,具有数百万门、编程灵活性较好、高级模块(PLL等)、IP保护和可扩展性强。

1.6 FPGA结构

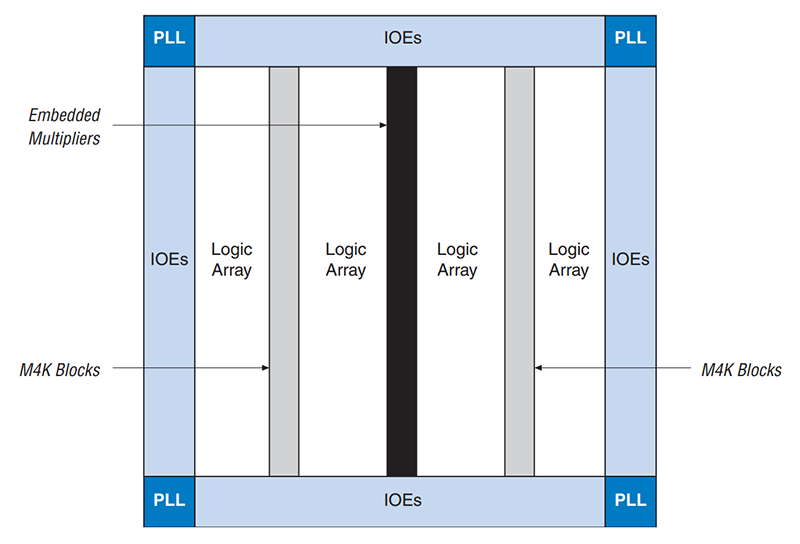

FPGA(Cyclone II EP2C20)结构包括逻辑单元LE(Logic Elements)组成的纵向的逻辑阵列;位于四周的输入输出单元IOEs;位于四角的锁相环PLL;存储器块(M4K blocks);DSP块(乘加器资源)。

1.7 FPGA逻辑单元LE

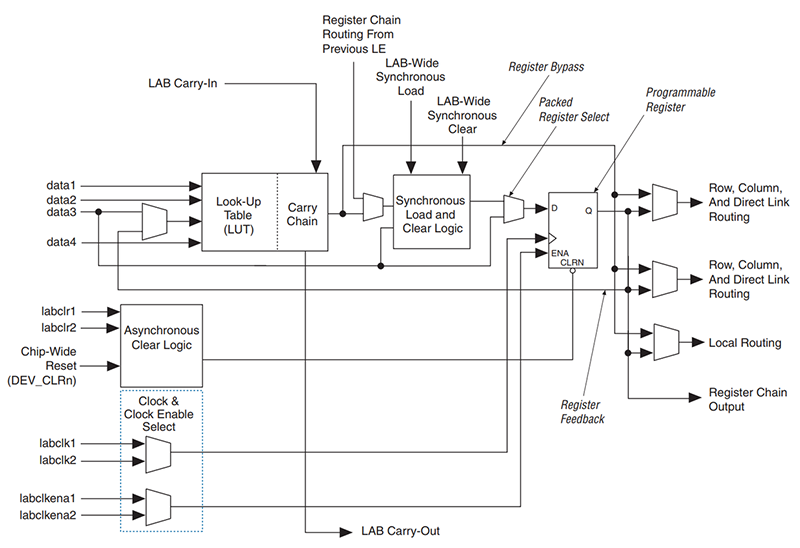

FPGA(Cyclone II EP2C20)逻辑单元包括四输入查找表;寄存器的同步装入和清除逻辑;可编程寄存器;路由器;异步清零逻辑;时钟管理逻辑。

1.8 FPGA查找表LUT

查找表原理为任意组合逻辑的乘积项SOP可用于对应的n输入多路器的实现。

多路器的选址端是逻辑的输入端,多路器的输出端是逻辑的输出端,多路器的输入端是用编程来实现真值表(基于RAM技术)。

1.9 FPGA高端应用

图像处理方面:模糊识别、3D技术、图像压缩、边缘检测技术、机器人视觉、虚拟现实和超现实技术。

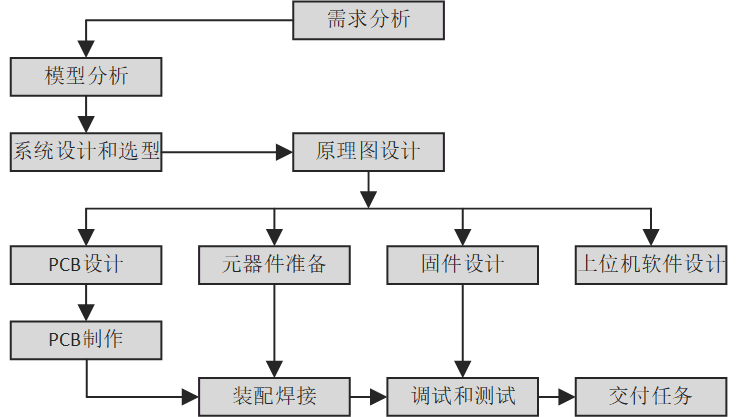

第2章 FPGA设计概述

2.1 工具与方法

数字设计电路设计工具HDL语言与ASIC/FPGA设计紧密相关,对应的CAD软件相继出现。

2.2 原理图到HDL

早期设计过程:

随着电子技术的进步,跟复杂庞大和精准有效的数字系统设计,则需要EDA(Electronic Design Automation)和CAD(Computer Aided Design)技术的帮助。

基于计算机语言的数字电路设计(硬件描述语言HDL),则能够方便快捷的完成从设计到验证的全过程。与其他类型的计算机语言不同,HDL语言着重在描述上,或者称为建模(Modeling)。

2.3 FPGA编程验证

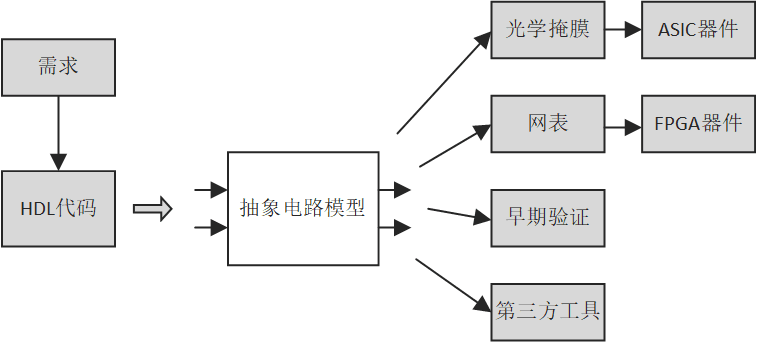

2.3.1 FPGA编译、映射与验证

用HDL描述的抽象硬件电路模型,Verilog称为Module,VHDL称为Component;FPGA是由许多单元(cells)组成,cell由LUT,IOE,Memory和DSP等构成;EDA首先将源HDL模型转变为基本的门级网表,称为编译(Compilation);EDA随后再为这些基本门模型分配具体的cell,称为映射(Mapping);为了验证抽象电路代码是否正确,则需要像真实电路那样,对其进行测试。这种对抽象电路模型进行的测试,称为验证(Verification);为了进行验证,需要单独编写一段HDL代码,建立一个用于测试目的的模型,称为Testbench。

2.3.2 验证模型Testbench

Testbench本质上仍旧是一段HDL建模代码,它本身不能运行,EDA软件提供了一种运行Testbench的方法,即按照电路模型机制,生成需要的激励信号并观察和分析模型中的信号,这种运行抽象模型的方法称为仿真(Simulation)。

- 综合前验证(Presynthesis Verification)时,Testbench加载的测试模型是用户RTL模型,而此时验证的内容主要是测试模型的逻辑性能,因此综合前验证又被称为功能仿真或RTL仿真(Function/RTLSimulation),有时也被简单地称为前仿(Presimulation)。

- 综合后验证(Postsynthesis Verification)时,Testbench加载的测试模型已经是装配后的由基本门描述的模型(gate-level),即网表(netlist),此时验证的内容主要是设计模型的时序性能,因此综合后验证又被称为时序仿真或门级仿真(Timing/Gate-levelSimulation),有时也被简单的称为后仿(Postsimulation)。

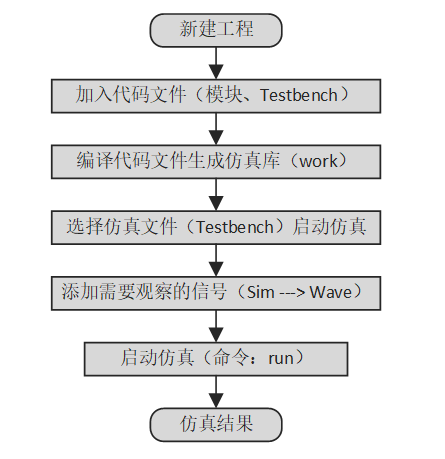

2.3.3 ModelSim验证

EDA仿真工具提供运行抽象电路模型的方法:根据描述生成对应的激励信号;对应组合逻辑的功能验证(Function Verification),根据组合逻辑函数的计算,可得到输出。组合逻辑的时序验证(Timing Verification),在功能验证基础上加入传输延迟,可得到输出;对应时序逻辑,仿真工具首先计算时钟,然后在每个沿上计算时序逻辑并发的结果,将其作为激励,在下一个沿上响应,以获得结果;仿真工具执行仿真前,将进行HDL的语法分析。执行仿真时,从顶层信号开始,按照层次化原则,逐层计算。计算结果以图表或报告的形式交互;仿真的理论依据遵从HDL数据流、行为和结构化建模理论。

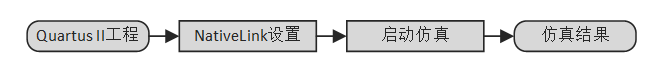

Altera的Quartus II提出一种一键启动的跨平台自动化方式,称其为NativeLink。使用NativeLink是要注意层次化设计(Top-Down),将需要测试的部件模型放入到当前工程的层次化中。

2.4 Verilog HDL设计流程

第3章 FPGA设计原则

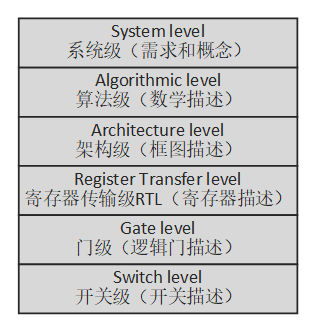

3.1 抽象层次

- 系统级(System-level):可以用高级别的语法描述需求和概念;

- 算法级(Algorithmic-level):可以将需求概念用数学形式描述;

- 架构级(Architecture-level):可以将逻辑用框图的形式描述;

- 寄存器传输级(RTL-level):可以用通用寄存器的传输操作来描述;

- 门级(Gate-level):可以将用寄存器描述的模型转变为用逻辑门描述的模型;

- 开关级(Switch-level):可以将逻辑门描述的模型转变为用电路开关描述的模型。

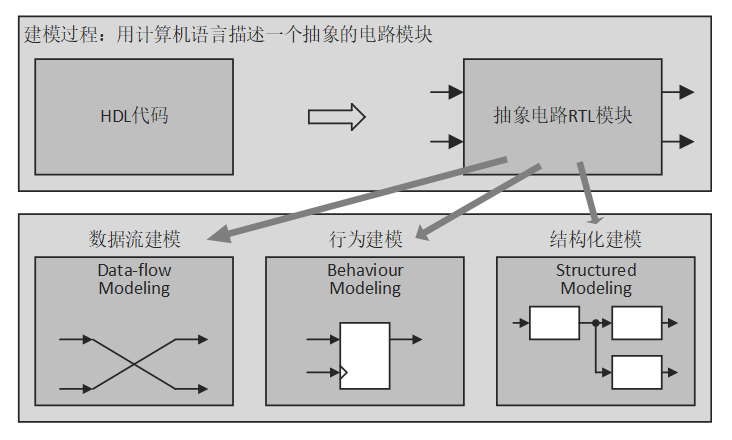

3.2 建模方式

3.2.1 数据流建模

在模块中对信号资源分配(或组合逻辑的连接)的描述,称为数据流描述(Data-flow Description),或称为数据流建模(Data-flow Modeling)。

3.2.2 行为建模

在模块中对信号的行为进行的描述,称为行为描述(Behavioral Description),或称为行为建模(Behavioral Modeling)。

3.2.3 结构化建模

将诸模块组织成一个更大的模块,其描述称为结构化描述(Structural Description),或称为结构化建模(Structural Modeling)。

3.3 建模过程

第4章 有限状态机设计

4.1 有限状态机概念

有限状态机FSM(Finite State Machine)用于描述各种复杂的时序行为,是使用HDL进行数字逻辑设计的重要方法之一。

基础为有限状态机FA(Finite Automata),由它延伸成的理论模型有:序列机SM(Sequential Machine),线性序列机LSM(Linear Sequential Machine)以及算法机ASM(Algorithmic State Machine)。实际工程中,FSM,LSM和ASM以及ASMD(Algorithmic State Machine and Datapath)或单独或组合使用。

LSM和ASM都是从FSM演变过来,有时广义上地将上述所有状态机统称为FSM。用于FSM的规划工具以及状态转移图STG(State Transition Graphs)和算法流程图ASMc(Algorithmic State Machine charts)应用较多,在LSM情况下,也可以用SMF表规划(Sequential Machine Flow)。

4.2 有限状态机类型

4.2.1 摩尔机(Moore Machine)

摩尔机的输出仅是状态的逻辑函数,其表达式为:

4.2.2 米利机(Mealy Machine)

米利机的输出是状态和输入的逻辑函数,表达式为:

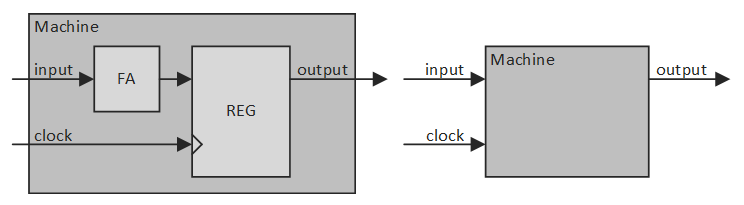

4.2.3 闭节点

时钟节点(Pipling Nodes)之闭节点(Closed Node)。

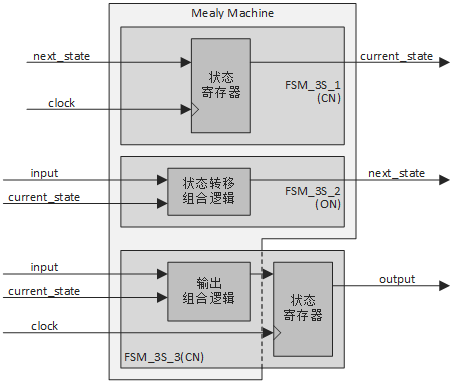

上图Out是同步信号(在当前时钟域的时钟参考点翻转),故Machine为一个时钟闭节点。右图为该机器的模块框图,同步信号用黑色表示,非同步信号用蓝色表示。

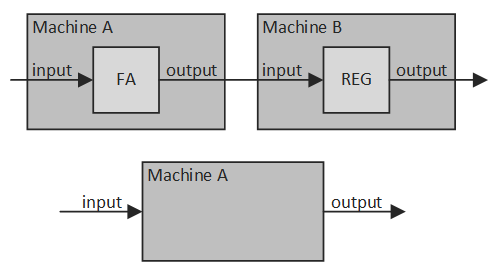

4.2.4 开节点

上图In和Out’是同步信号, In’和Out为非同步信号,故MachineA构成一个时钟开节点。时钟开节点机器需要在下游插入寄存器以恢复时钟信号,这被用于计算和考虑传输延迟。

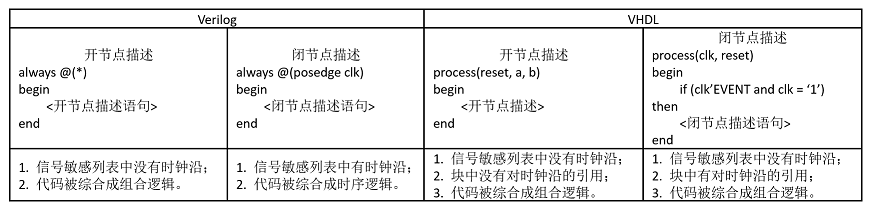

4.2.5 时钟节点与代码的关系

4.3 有限状态机形式

4.3.1 一段式状态机(时钟闭节点机器)

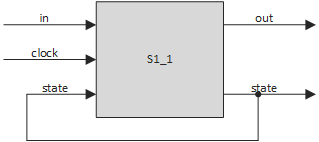

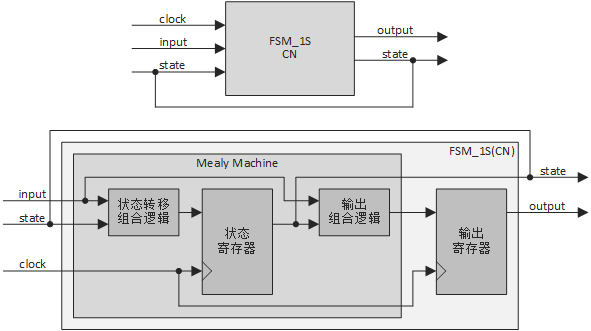

在同一个always块中编写;输出为同步信号,既时钟闭节点,因此务必使用posedge clock为敏感信号;由于输出state为同步信号,因此state可以闭合,满足一个时钟后响应的要求。

4.3.2 二段式状态机(时钟开节点机器)

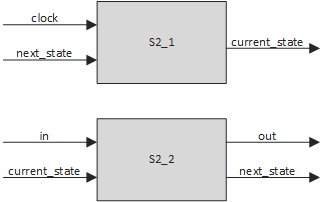

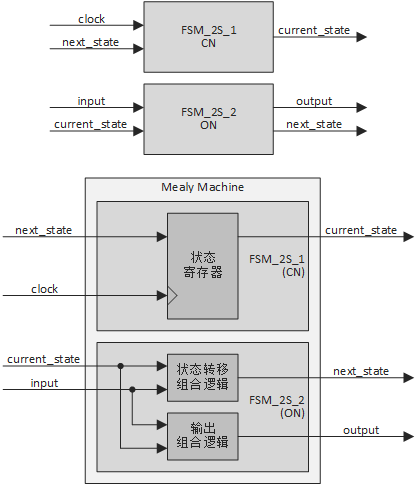

用两个always分别描述S2_1和S2_2;S2_1输出current_state为同步信号,要求posedge clock为敏感信号;S2_2为组合逻辑,输出的Out为非同步信号,既时钟开节点机器(要求Out下游插入寄存器)。

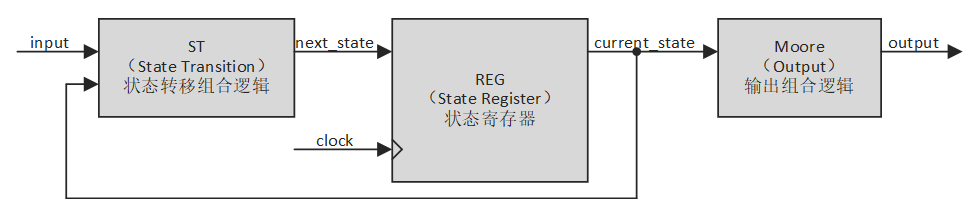

4.3.3 三段式状态机(时间闭节点机器)

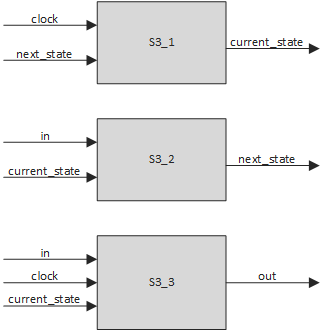

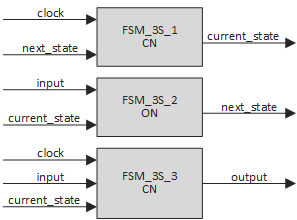

用三个always分别描述S3_1和S3_2和S3_3;S3_1输出current_state为同步信号,要求posedge clock为敏感信号;S2_2为组合逻辑,输出的next_state为非同步信号;S3_3输出Out为同步信号,要求posedge clock为敏感信号。

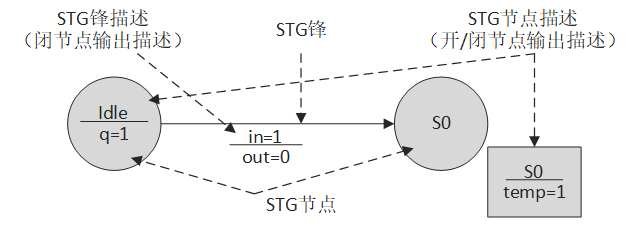

4.4 状态转移图STG

锋(edge)表示状态转移,锋的描述部分是对同步逻辑信号或闭节点信号的描述,用放置在对应锋附近的一个分数形式表示:分子为输入或条件,分母为输出或驱动。

节点(node)表示状态,节点的描述部分是对组合逻辑信号或闭节点信号的描述,用放置在对应节点附近的一个矩形框表示:矩形框内的分子为节点名,分母为输出或驱动。

无条件的锋描述时(仅有分母的描述),分子可用“*”号表示分子。

无驱动的描述时(仅有分子的描述),分数线可省略。

输出信号没有新的驱动时,对该信号的描述可省略。

将复位视作一种状态进行描述,但是复位引起的状态转移则省略。同步复位用锋描述,异步复位用节点描述。