Reference

- ARM Datasheet

Generic Interrupt Controller v3-and-v4-overview.pdf

GICv3_Software_Overview_Official_Release_B.pdf

Arm Generic Interrupt Controller Architecture Specification GICv3v4.pdf

Background (Why)

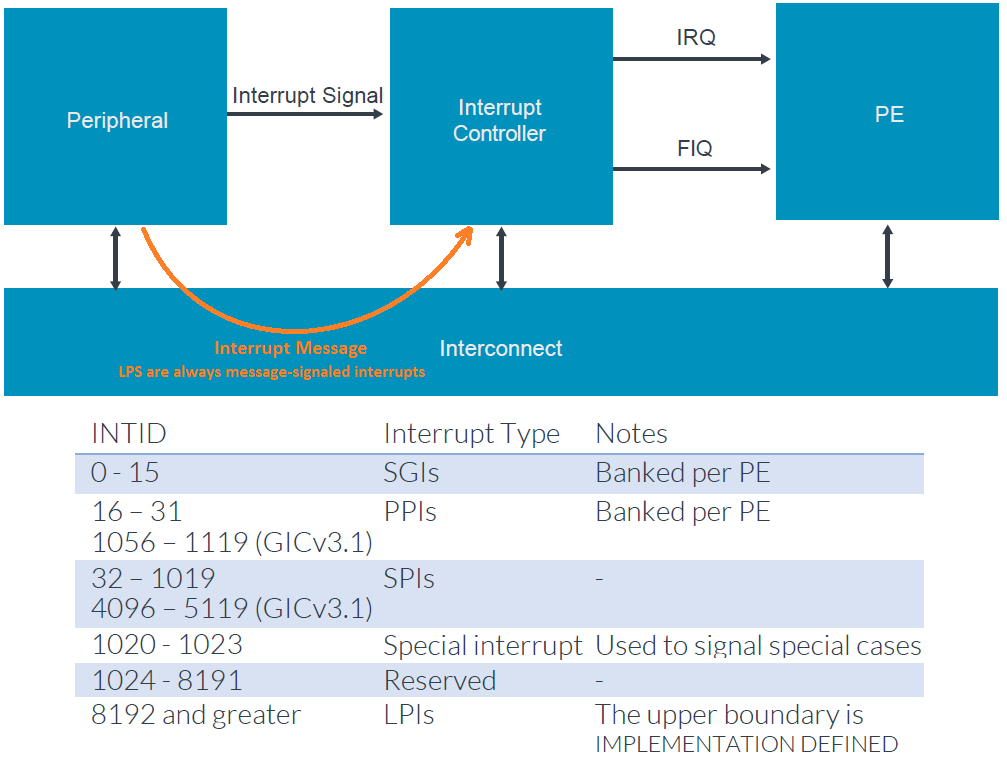

Processor has to handle events (i.e. interrupts) reported from devices and other processors. Interrupt Controller (such as GICV3, APIC) is necessary infrastructure for the processor.

GICv3v4 Overview (What)

- A Generic Interrupt Controller (GIC) takes interrupts from peripherals, prioritizes them, and delivers them to the appropriate processor core.

- The GIC is the standard interrupt controller for Arm Cortex-A and Arm Cortex-R profile processors. The GIC provides a flexible and scalable approach to interrupt management, supporting systems with a single core to large multi-chip designs with hundreds of cores.

- Interrupt Types

- Interrupt State Machine

- Timer Interrupts

- Security Model

- Programmer Model

- Prioritization (TBD)

- Affinity routing (TBD)

-

Interrupt Types and Signaling Path

IRQ stands for Interrupt ReQuest

- FIQ stands for Fast Interrupt reQuest

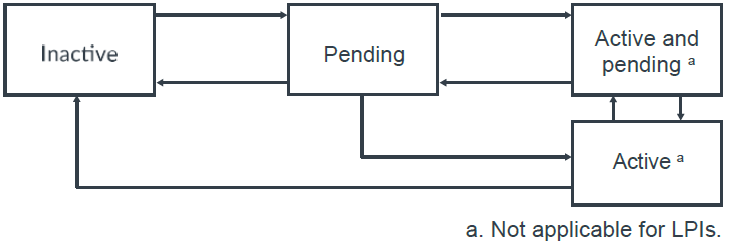

Interrupt State Machine (How)

- Inactive

Interrupt source is not currently asserted.

- Pending

Interrupt source has been asserted, but the interrupt has not yet been acknowledged by a PE.

- Active

Interrupt source has been asserted, and the interrupt has been acknowledged by a PE.

- Active and Pending

An instance of the interrupt has been acknowledged, and another instance is now pending.

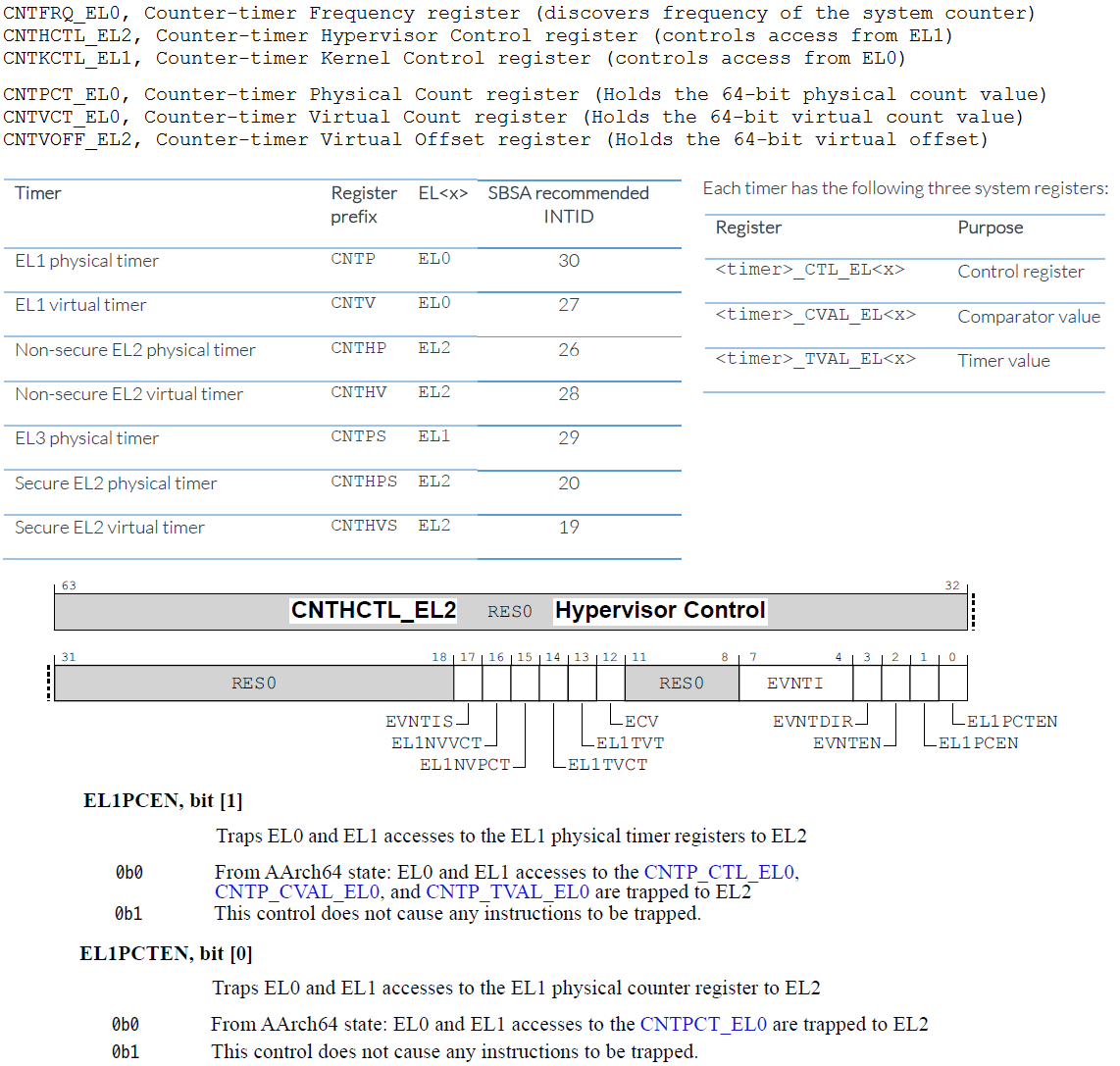

Time Interrupts (How)

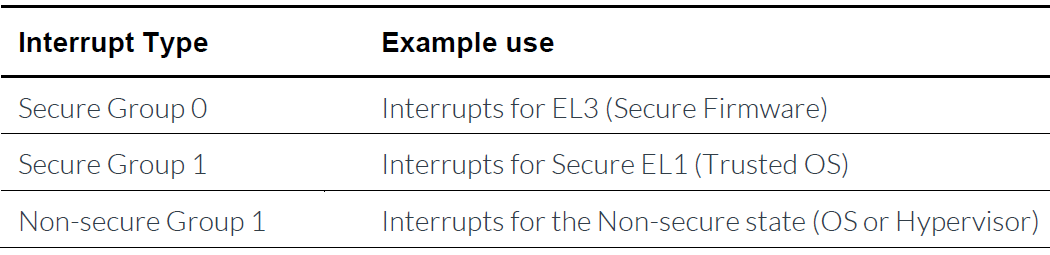

Security Model (How)

- The Arm GICv3 architecture supports Arm TrustZone technology. Each INTID must be assigned a group and security setting by software.

- GICv3 supports three combinations of settings, as you can see in the following table

- Use of TrustZone is OPTIONAL. This means that you can configure your implementation to have either a single Security state or two Security states. Typically, this means that the GIC will support two Security states when connected to Arm Cortex-A profile processors and one Security state when connected to Arm Cortex- R profile processors.

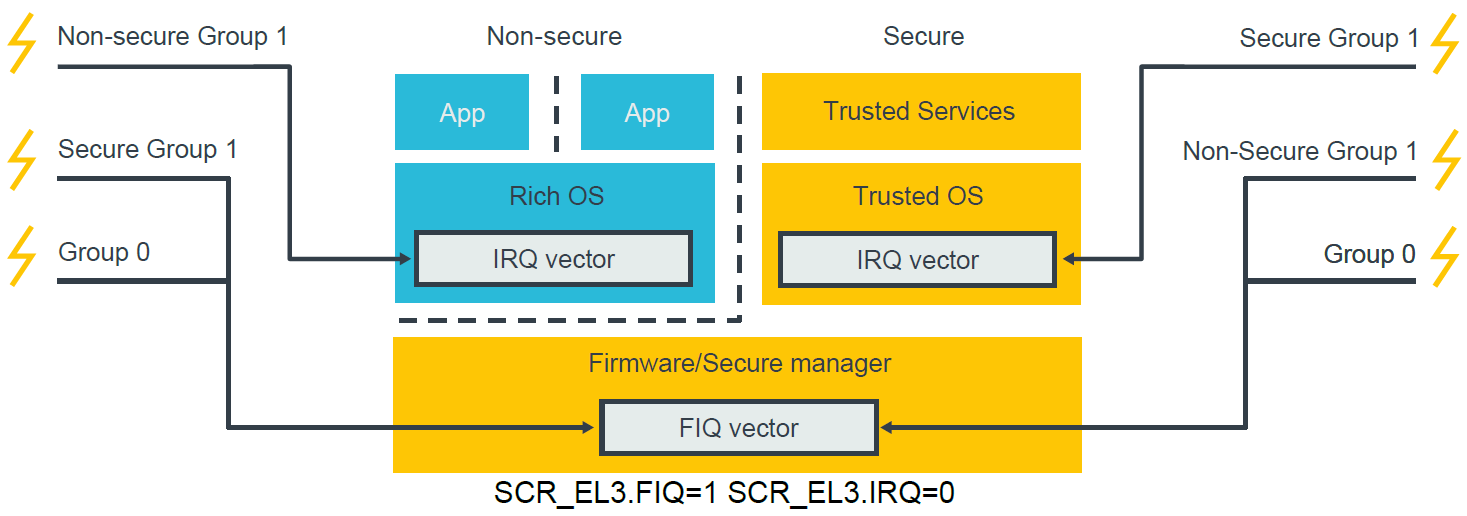

Programmer Model (How)

Register Interface

- Distributor interface

The Distributor registers are memory-mapped and used to configure SPIs.

- Redistributor interface

There is one Redistributor per connected core. It is used to configure SGIs & PPIs.

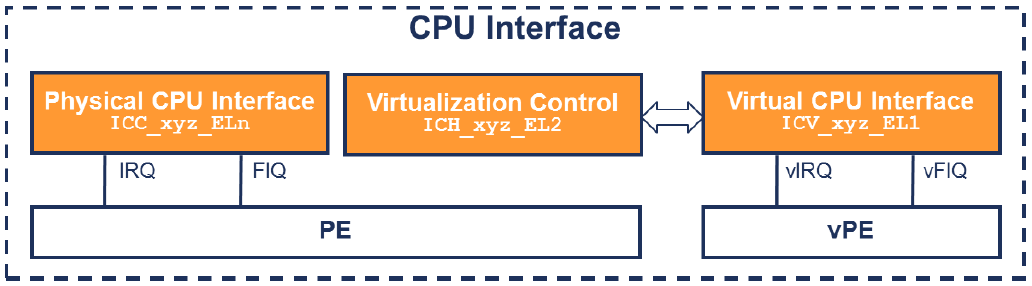

- CPU interface

Each core contains a CPU interface, which are system registers that are used during interrupt handling.

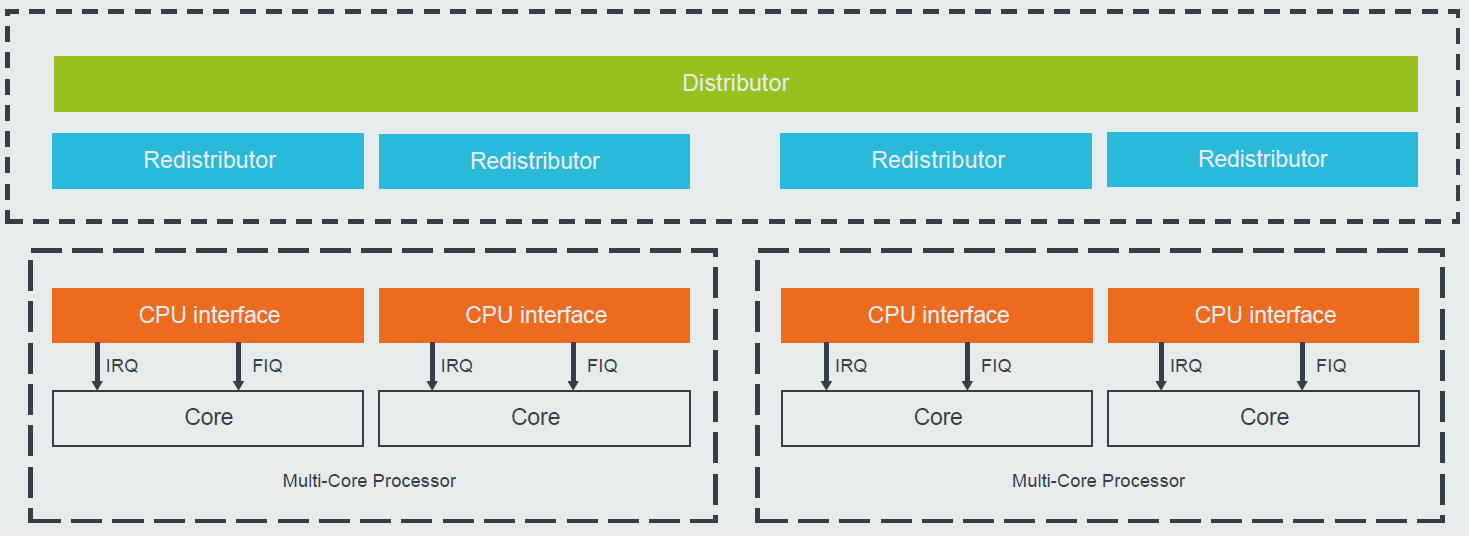

CPU Interface for Virtualization

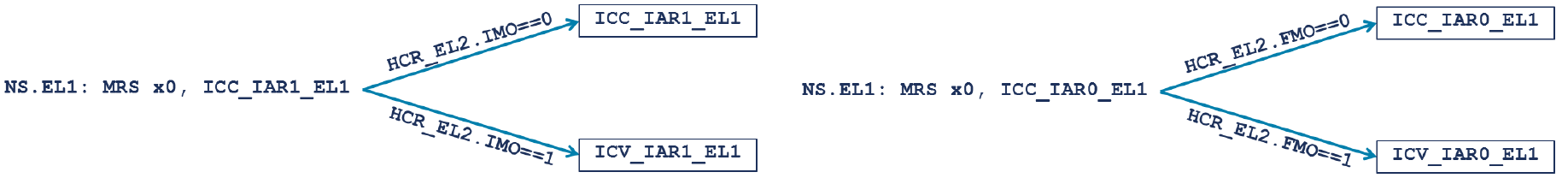

- Software executing in a virtualizaed environment uses the ICV*_EL1 registers to handle interrupts. These registers have the same format and function as the ICC*_EL1 registers.

- At EL2, EL3 and Secure EL1, the ICC registers are always accessed. At Non-secure EL1, whether the ICC or the ICV registers are accessed is determined by the routing bits in HCR_EL2. When HCR_EL2.IMO==1 or HCR_EL2.FMO==1, ICV registers, instead of ICC registers, are accessed at Non-secure EL1.