计算机系统的层次结构

自顶向下的结构

计算机系统的固定的层次结构,促使了我们写的每一行代码都按照固定的顺序往下去层层翻译,最终被系统识别并执行。其顺序结构如下:

软件:

- 虚拟机器M4(高级语言机器):用编译程序翻译成汇编语言程序

- 虚拟机器M3(汇编语言机器):用汇编程序翻译成机器语言程序

- 虚拟机器M2(操作系统机器):向上提供”广义指令”(系统调用)

硬件:

- 传统机器M1(用机器语言的机器):执行二进制机器指令

- 微程序机器M0():由硬件直接执行微指令

计算机硬件的基本组成

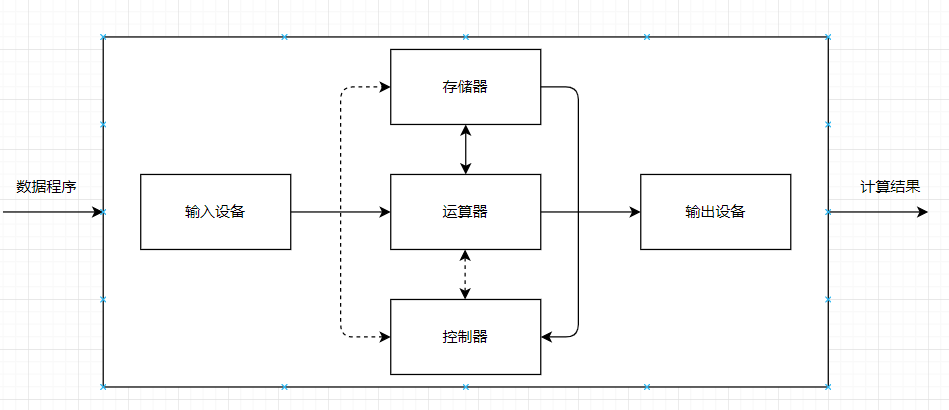

冯诺依曼机的结构

1、计算机由五个部件组成

2、指令和数据以同等地位存于存储器,可按地址寻访

3、指令跟数据用二进制表示

4、指令由操作码跟地址码组成

5、以运算器为中心,输入设备存储数据是通过运算器转发给存储器

现代计算机的结构

现代计算机主要由cpu+主存储器组成。

cpu

cpu主要包括运算器跟控制器两大部分,此外,还包括若干个寄存器和高速缓存存储器,用内部总线连接。

cpu有四个基本的功能:

- 指令控制 程序的顺序控制,保证机器按照顺序执行程序。

- 操作控制 一条指令的功能往往是由多个操作信号的组合来实现的,cpu管理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应的部件,从而控制这些部件按指令的要求进行动作。

- 时间控制 对各种操作实施时间上的定时。

- 数据加工 对数据进行算术运算跟逻辑运算处理,是cpu的根本任务。

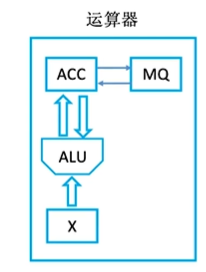

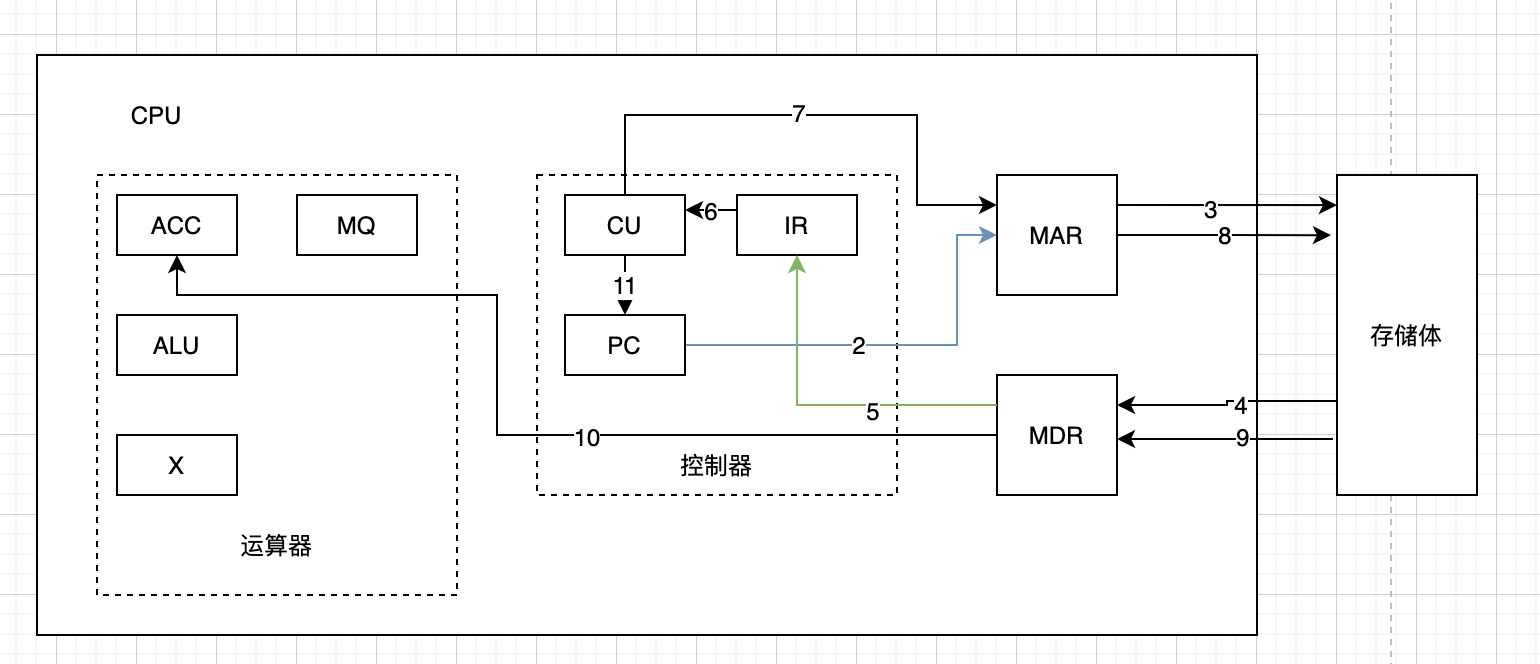

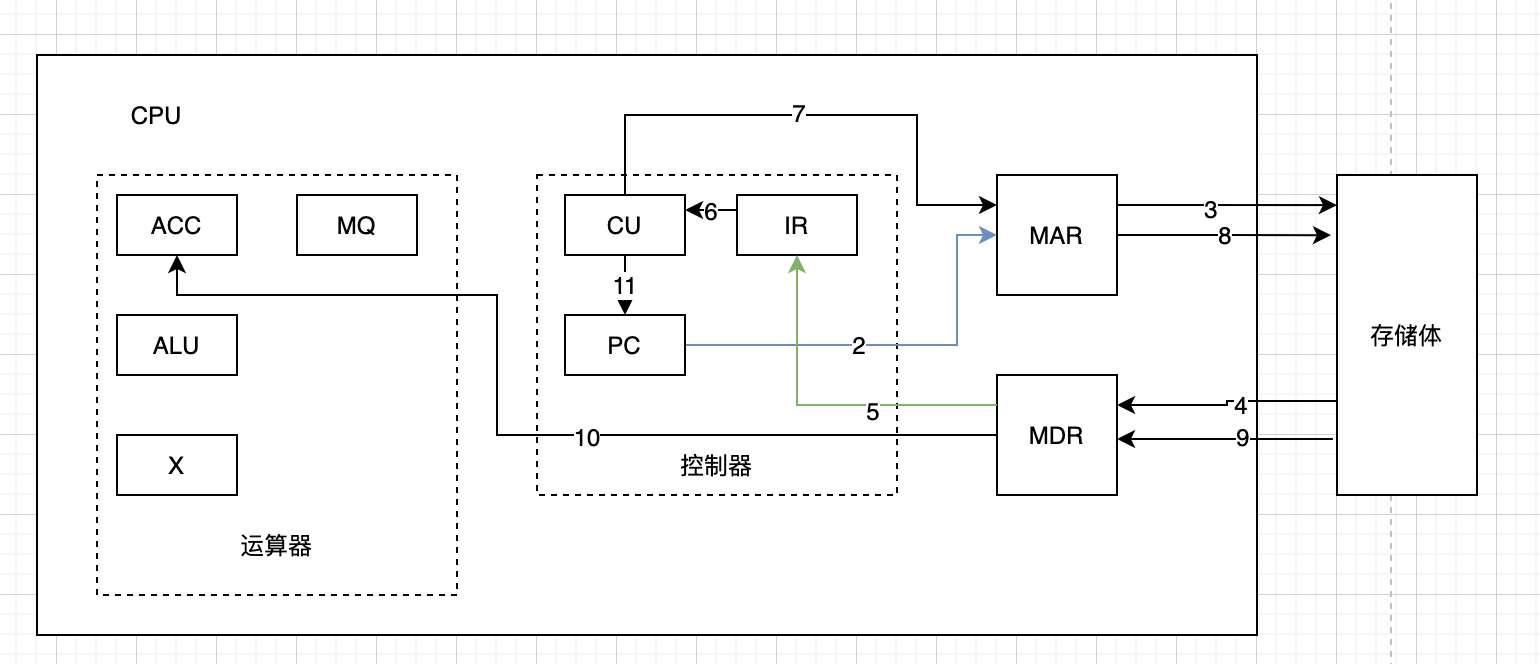

运算器

用于实现算术运算、逻辑运算(如:与、非等)

在通用的概念上面,运算器指的是运算逻辑部件ALU一个,但需要完成运算逻辑需要与其他寄存器协作,于是运算器的组成也可以描述成由ACC、MQ、X、ALU等组成(在不同的cpu上可能寄存器也有所不同)

ACC: 累加器,用于存放操作数,或运算结果

MQ:乘商寄存器,在乘、除运算时,用于存放操作数或者运算结果

X:通用的操作数寄存器,用于存放操作数

ALU:算术逻辑单元,通过内部复杂的电路实现算数运算、逻辑运算

在四则运算过程中,会有三个参数在运算器中进行不同位置的存储

ACC:被加数、和、被减数、差、乘积高位、被除数、余数

MQ: 乘数、乘积地位、商

X:加数、减数、被乘数、除数

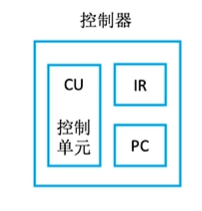

控制器

与运算器的概念雷同,关键是控制单元部件PU,这里一样以CU、IR、PC为一个整体控制器。

CU: 控制单元,分析指令,给出控制信号

IR: 指令寄存器,存放当前执行的指令

PC: 程序计数器,存放下一条指令地址,有自动加1功能

寄存器

MAR、MDR

MAR:Memory Address Register,也就是地址寄存器,MAR位数反映了存储单元的个数

MDR:Memory Data Register,也就是数据存储器

当cpu需要从存储体操作数据时,会传给MAR 物理地址,主存储器再把对应的数据传给MDR,MDR再传回给相应的部件

存储器

存储器分为主存跟辅存,主存就是主存储器,而辅存相当于I/O设备比如机械硬盘等外部存储器

主存储器

主存储器主要指的是存储体

- 存储体:地址 + 存储单元 组成

- 存储单元:由多个存储元件组成,存储的一串二进制代码。MAR位数反映了存储单元的个数, 而MAD则是存储单元的长度

- 存储元件:存储二级制的电子元件,每个可存1bit数据量

- 存储字:存储单元中二进制代码的组合

- 存储字长: 存储单元中二进制代码的位数

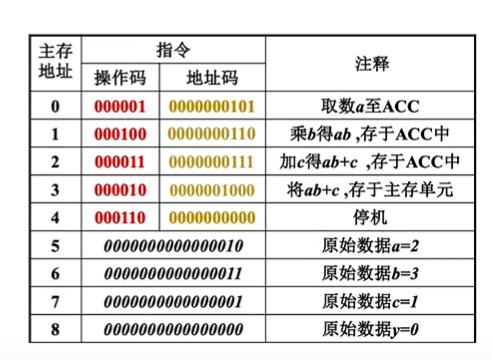

协同工作过程的例子

现在有如下的代码,忽略其他必须的代码,保留最核心的。

// 初始化参数

int a=2,b=3,c=1,y=0

// 计算逻辑

y = a*b+c

上面的代码进行编译后,会装入主存中,其存储的形式如下:

执行过程:

1、(PC)=0,指向第一条指令的存储地址

2、CPU根据PC把0传给MAR, (MAR)=0

3、MAR把存储地址传给存储体M

4、M(MAR)再把主存地址为0的数据取出,然后传给MDR,使得(MDR)= 000001 00000000101

5、(MDR)把数据传给IR,使得(IR)=000001 0000000000101

6、IR拆解出操作码(也叫OP码)与地址码,然后把操作码000001送到CU,通过对操作码的分析得出这是一个“取数”指令

7、于是IR把地址码00000000101=5发给MAR,使得MAR=5

8、MAR把存储地址传给存储体M

9、M(MAR)再把存储地址为5的数据取出,然后传给MDR,使得(MDR)= 000000 00000000010

10、因为是取数指令,所以MDR会把数值传给ACC, 导致ACC=000000000010=2

11、取数指令执行完毕后,CU会指挥PC进行递增,指向下一条指令的存储地址。

12、然后就是重复2-9的步骤去执行,直到停止指令操作。

下图为具体的流程图:

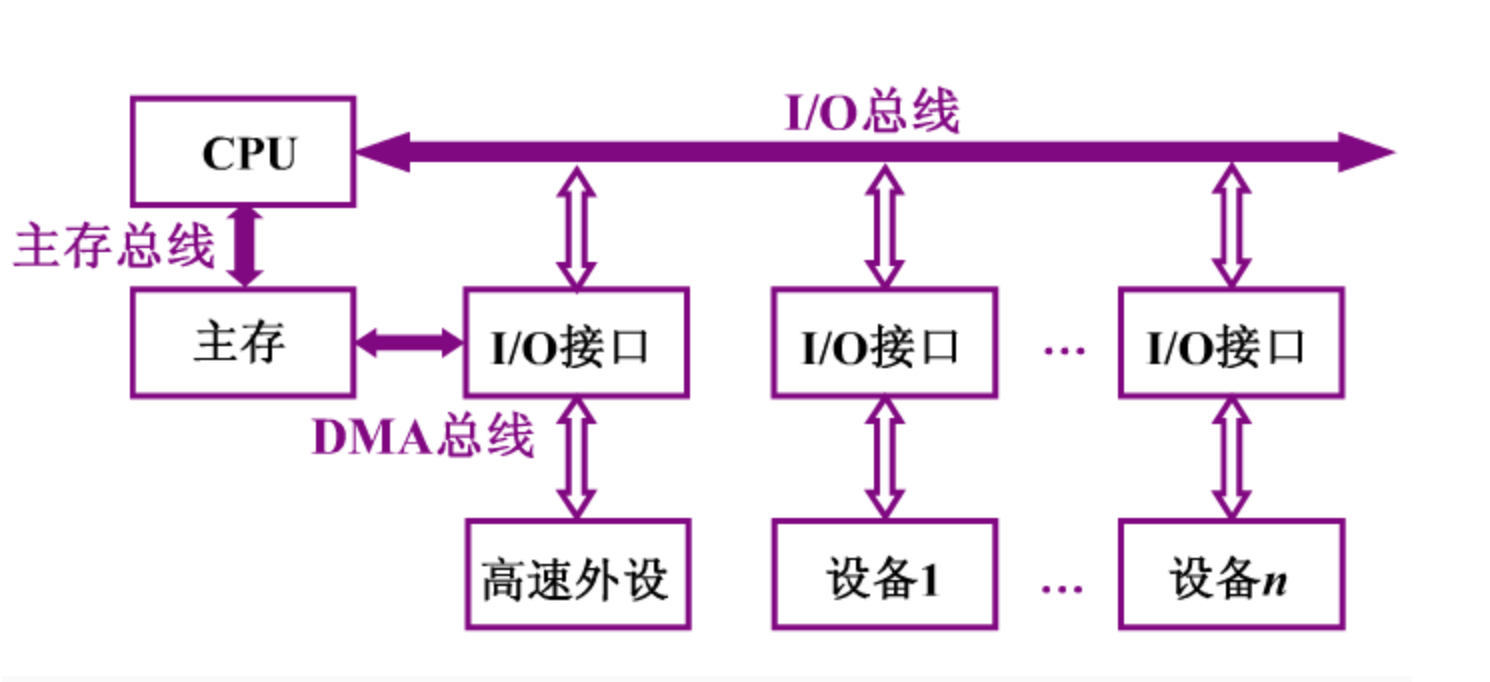

DMA

DMA(Direct Memory Access),即直接存储器存取,是一种完全由硬件执行I/O交换的工作方式。比如希望外设A 的数据拷贝到外设 B,只要给两种外设提供一条数据通路,再加上一些控制转移的部件就可以完成数据的拷贝。DMA控制器从CPU完全接管对总线的控制。数据交换不经过CPU,而直接在内存和I/O设备之间进行。由于CPU不参与传送操作,所以就可以省去了CPU取指令、取数、送数等操作。整个数据传输操作在一个 DMA 控制器(DMAC)的控制下进行的,CPU 除了在数据传输开始和结束时做一点处理外(开始和结束时候要做中断处理),在传输过程中 CPU 可以继续进行其他的工作。这样在大部分时间里,CPU 计算和 I/O 操作都处于并行操作,使整个计算机系统的效率大大提高。

在经常提及的零拷贝的概念中就用上了DMA。

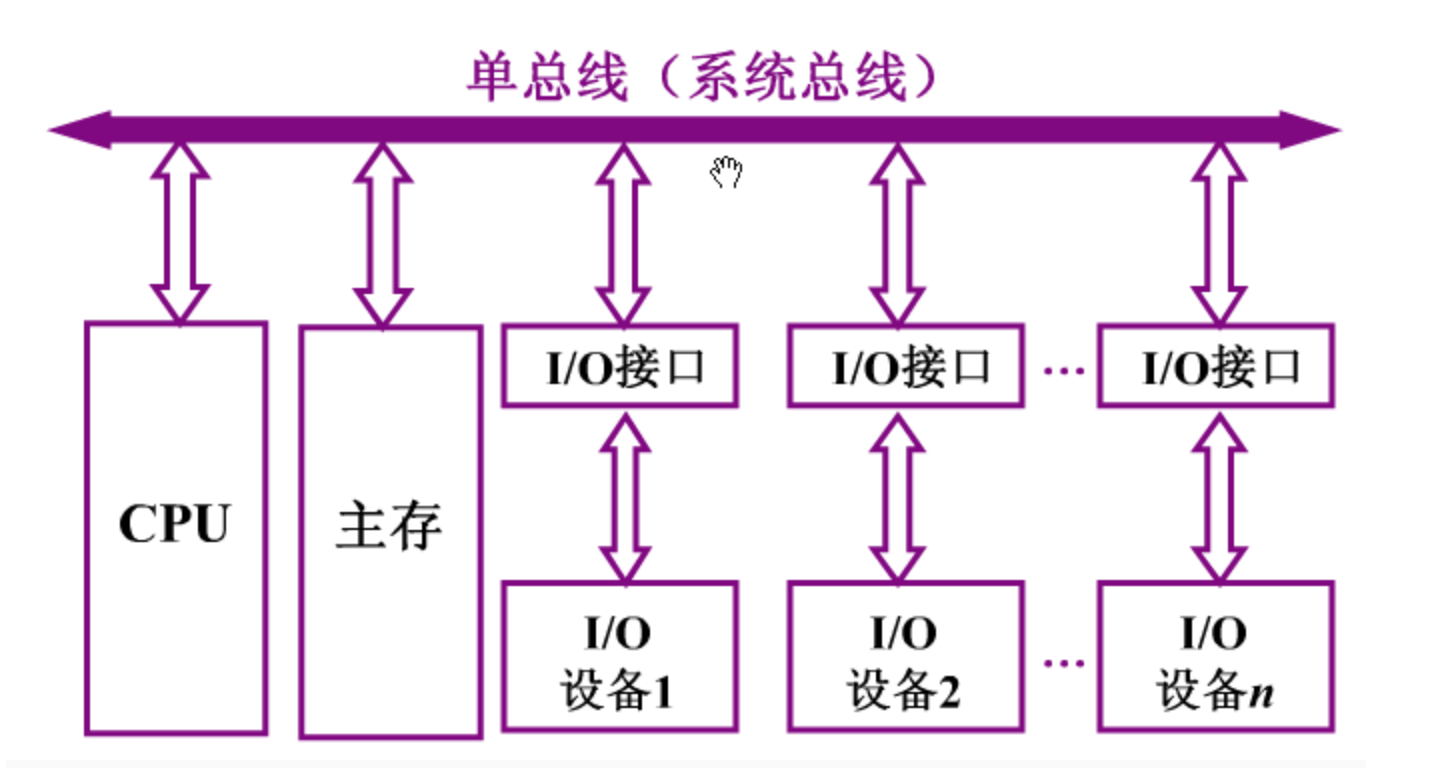

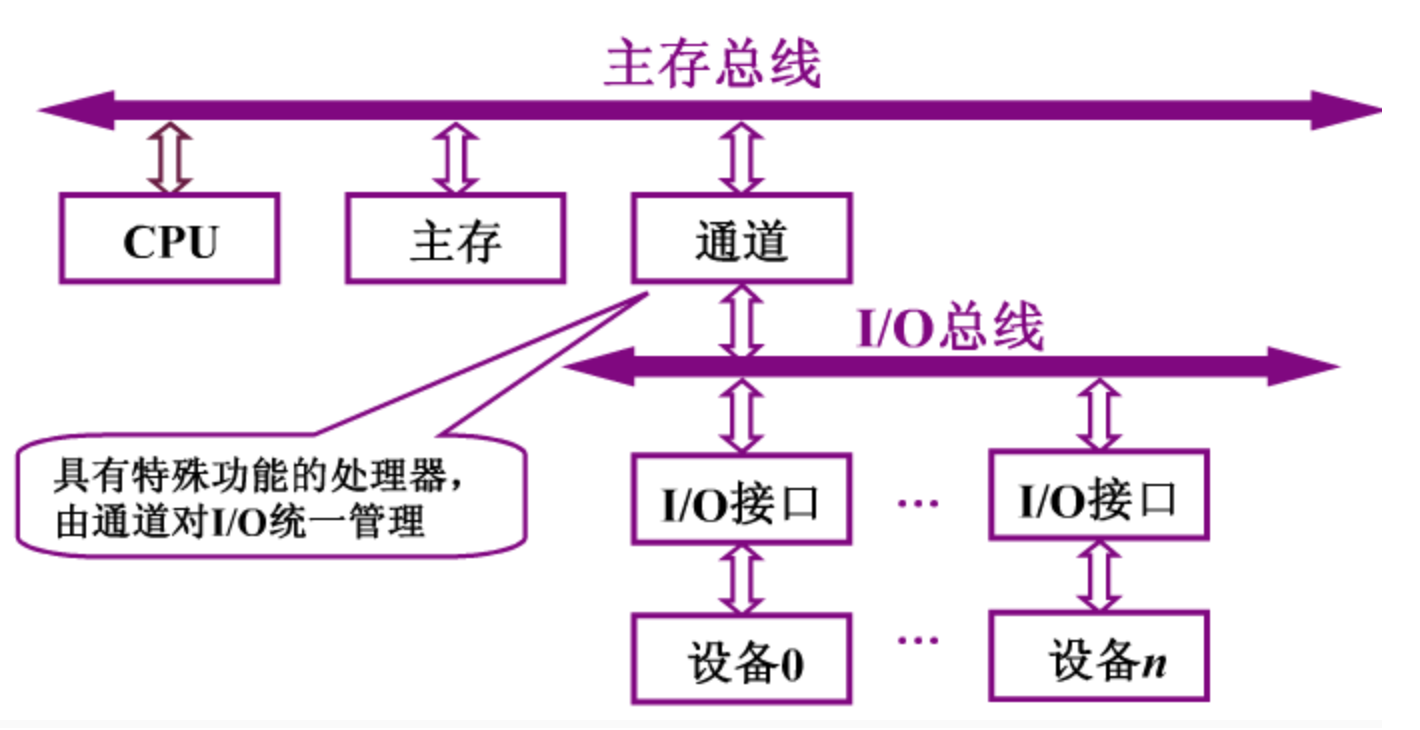

总线

总线是构成计算机系统的互联机构,是多个系统功能部件之间进行数据传送的公共通路。借助于总线连接,计算机在各系统功能部件之间实现地址、数据和控制信息的交换,并在争用资源的基础上进行工作。

一个单处理器系统中的总线,大致分为三种:

1、CPU内部连接各寄存器及运算部件之间的总线,称为片内总线、内部总线等。

2、CPU同计算机系统的其他高速功能部件,如存储器、通道等互相连接的总线,称为系统总线。

3、中、低速I/O设备之间互相连接的总线,称为通信总线、外部总线、I/O总线等。

其中关心的主要是系统总线,它又分为数据总线、地址总线和控制总线。

- 数据总线(Data Bus):在CPU与RAM之间来回传送需要处理或需要储存的数据。

- 地址总线(Address Bus):用来指定在RAM之中储存的数据的地址。

- 控制总线(Control Bus):将微处理器控制单元的信号,传送到周边设备。

结合上面的工作过程的例子,可知下图中,3、8属于地址总线,4、9属于数据总线

单总线结构图

双总线结构图

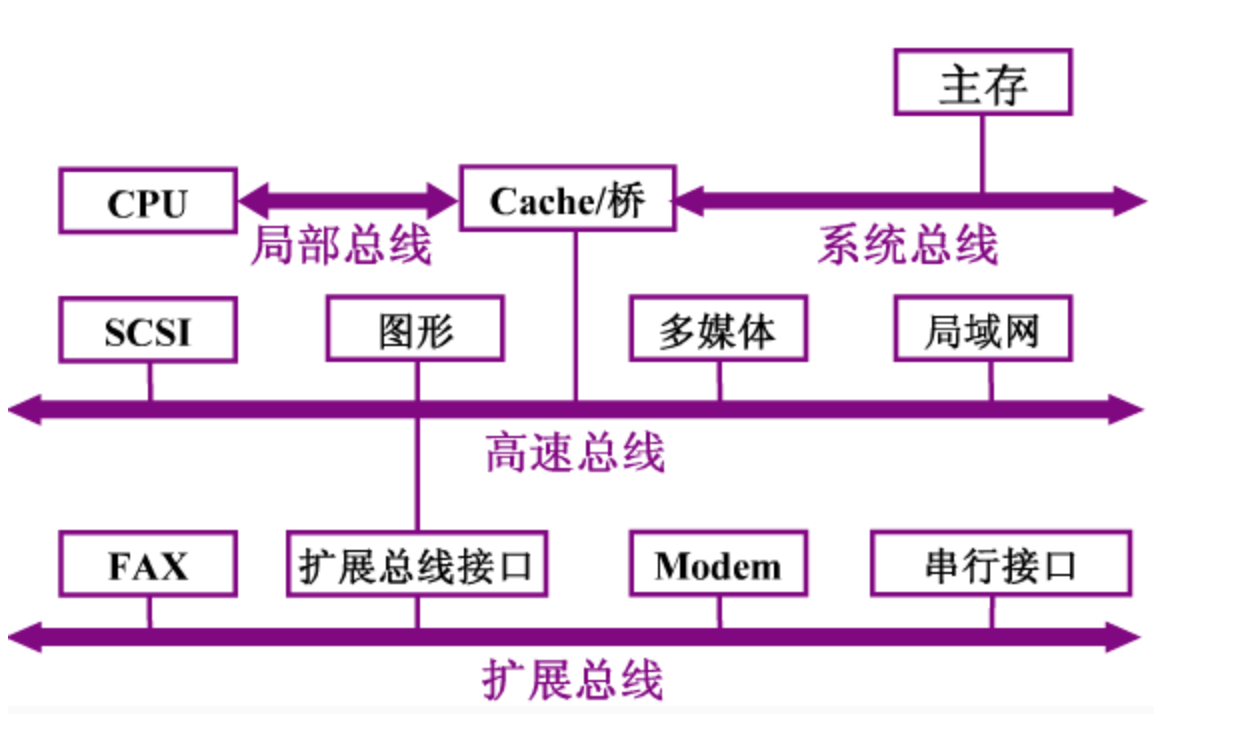

三总线结构图

四总线结构图

总线仲裁

集中仲裁方式

由总线控制器的判优、仲裁逻辑按一定的优先级顺序确定哪个主设备能使用总线。每个功能块有两条线连到总线控制器,一条是送往仲裁器的总线请求信号线BR,一条是仲裁器送出的总线授权信号线BG。有三种方式:

- 链式查询方式:BG串行地从一个I/O接口传到下个I/O接口,假如到达的接口无总线请求就到下个接口直到有就停止查询,授权该接口请求总线。所以靠近仲裁器的接口有优先级。

- 计数器定时查询方式:不做解释,没人使用。

- 独立请求方式:每一个设备都有一对BR、BG,而仲裁器有一个排队电路,它根据一定的优先次序决定首先响应的设备,当代总线标准普遍采用它。

分布仲裁方式

不需要中央仲裁器,每个潜在的主模块都有自己的仲裁器和仲裁号,多个仲裁器竞争使用总线。

当设备有总线请求时,它们就把各自唯一的仲裁号发送到共享的仲裁总线上;每个仲裁器将从仲裁总线上得到的仲裁号与自己的仲裁号进行比较;如果仲裁总线上的号优先级较高,则不予响应并撤销它的仲裁号;最后获胜的仲裁号保留在仲裁总线上。