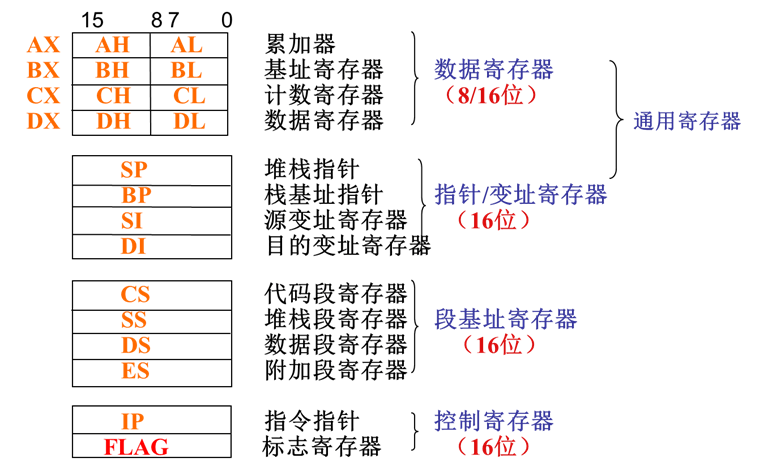

寄存器&标志位

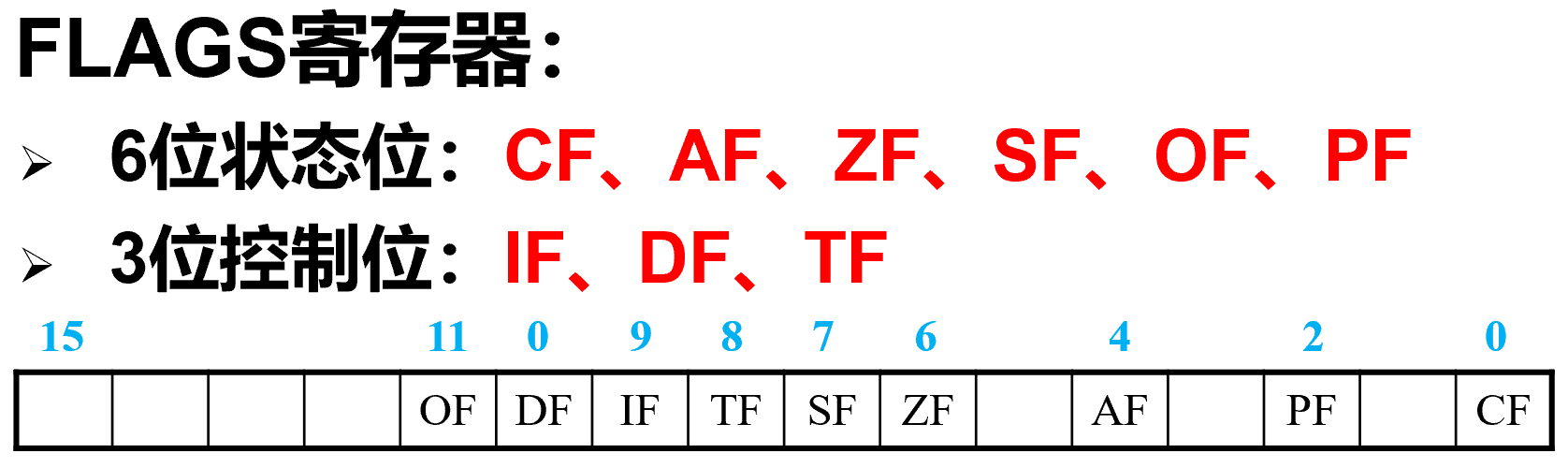

FLAGS寄存器报告正在执行的程序的状态,并允许有限地(应用程序级)控制处理器。

IP寄存器包括下一条要执行的指令的16位指针。

存储器寻址规定偏移量

SP**寄存器不能用作索引寄存器;

当SP或BP寄存器用作为基地址,SS段是默认的段;在其他情况下DS段是默认段。

小端方式:小地址放低位

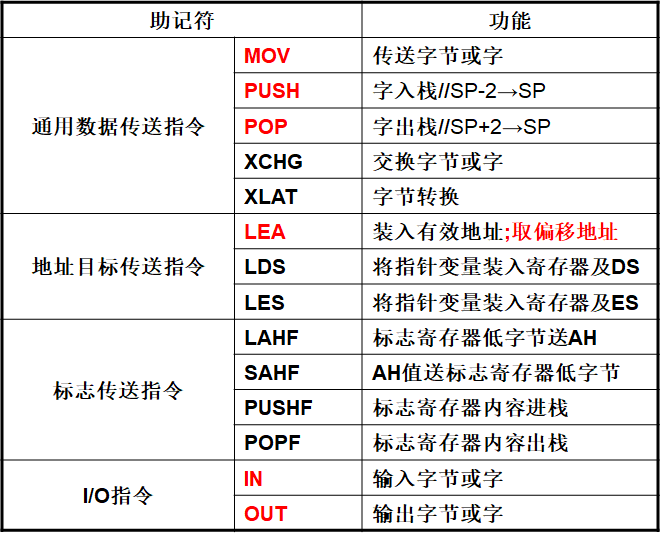

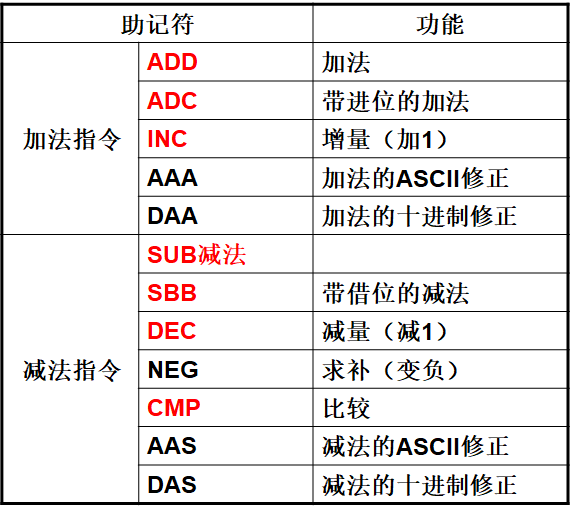

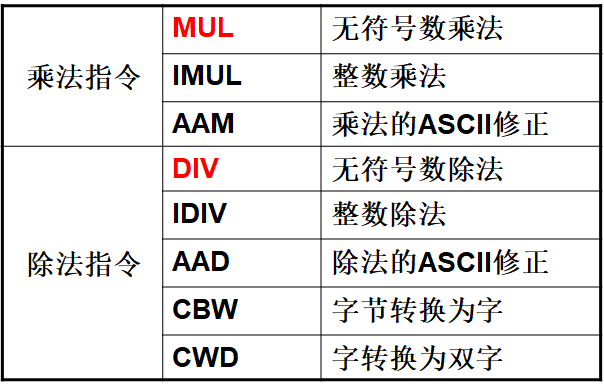

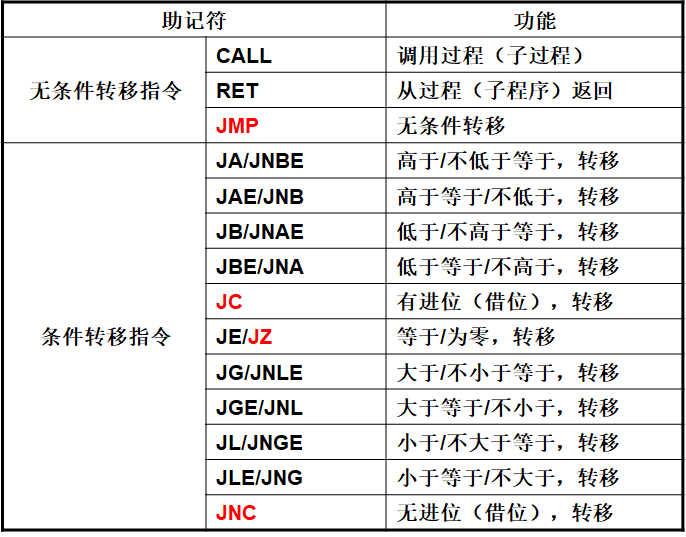

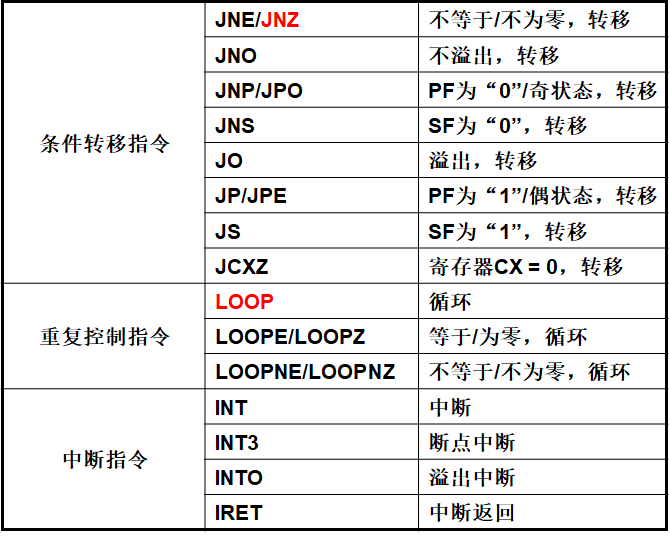

汇编指令

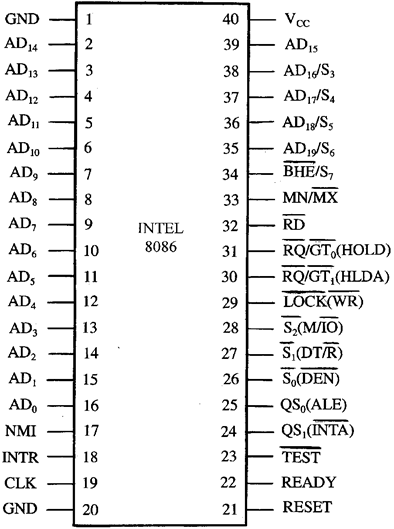

8086

引脚和功能:https://blog.csdn.net/ww7510/article/details/82355887

40条引线,按照功能:地址、数据、控制、其他(时钟与电源) (括号中为最小组态下名称)

(括号中为最小组态下名称)

部分引脚

AD ~ AD:地址/数据总线->T1:用作低 16 位地址 A ~ A0;T2 ~ T4:用作数据总线 写**信号,低电平有效

写**信号,低电平有效 读选通信号,低电平有效

读选通信号,低电平有效

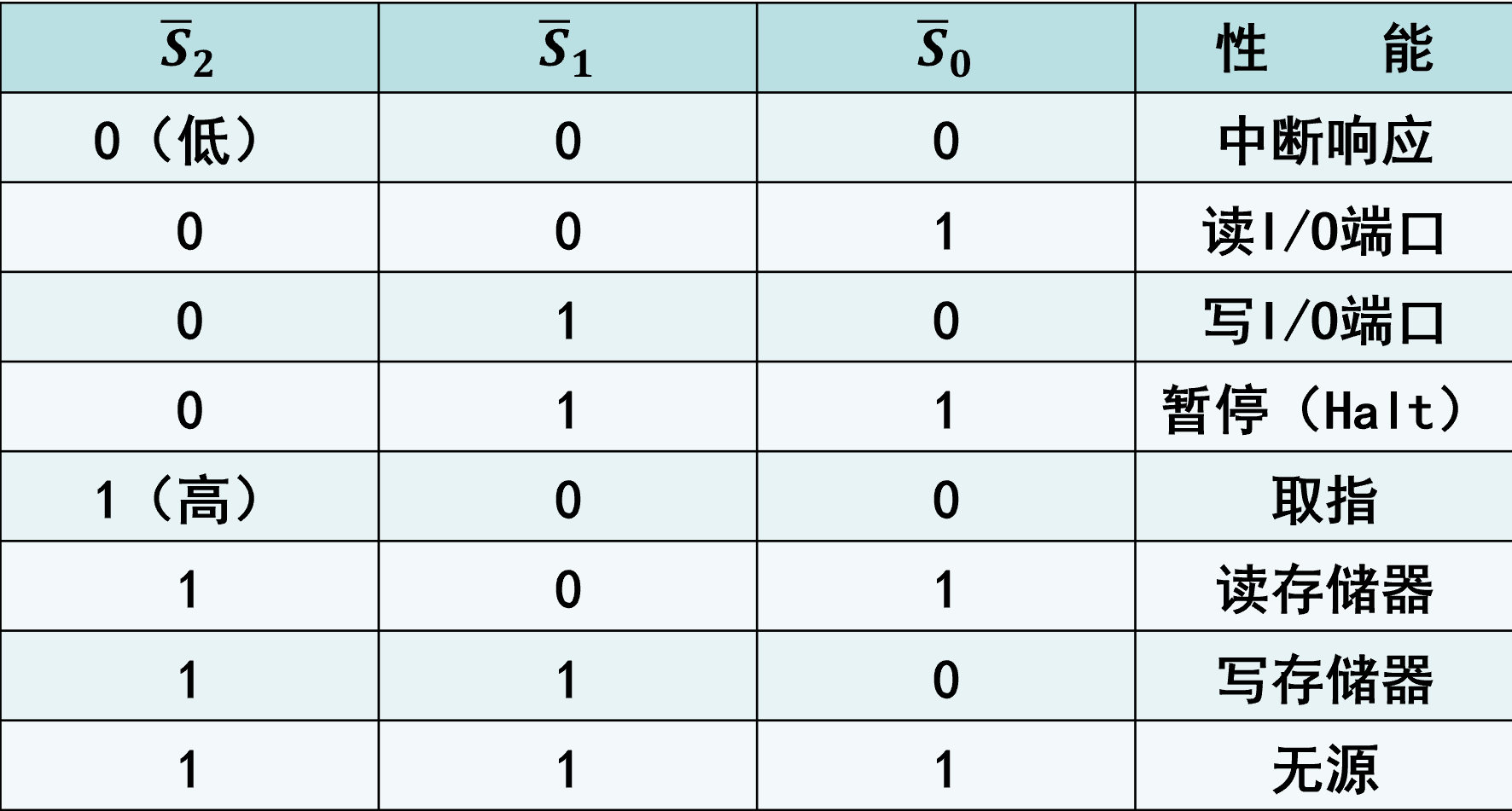

读写的具体操作取决于 引脚信号

引脚信号 存储器/IO控制信号;用于区分CPU是访问存储器(高电平)还是访问I/O端口(低电平)

存储器/IO控制信号;用于区分CPU是访问存储器(高电平)还是访问I/O端口(低电平) 地址锁存信号;

地址锁存信号;

8086CPU在总线周期的第一个时钟周期内发出的正脉冲信号,其下降沿用来把地址/数据总线(AD15~AD0)以及地址/状态总线(A19/S6~A16/S3)中的地址信息锁住存入地址锁存器中。 可屏蔽中断请求信号;(输入)

可屏蔽中断请求信号;(输入)

电平触发输入信号,高电平有效,只要检测到高电平就一直触发中断。

CPU在每一个指令周期的最后一个T状态采样INTR以决定是否进入中断响应周期。 中断响应信号;

中断响应信号;

当8086响应来自INTR引脚的可屏蔽中断请求时,在中断相应周期内,INTA变为低电平。 非屏蔽中断输入信号;(输入)

非屏蔽中断输入信号;(输入)

边沿触发信号,当引线电平出现由低到高变化时,将在当前指令结束以后引起中断;

NMI引线的中断请求信号不能用软件加以屏蔽。**

最大组态

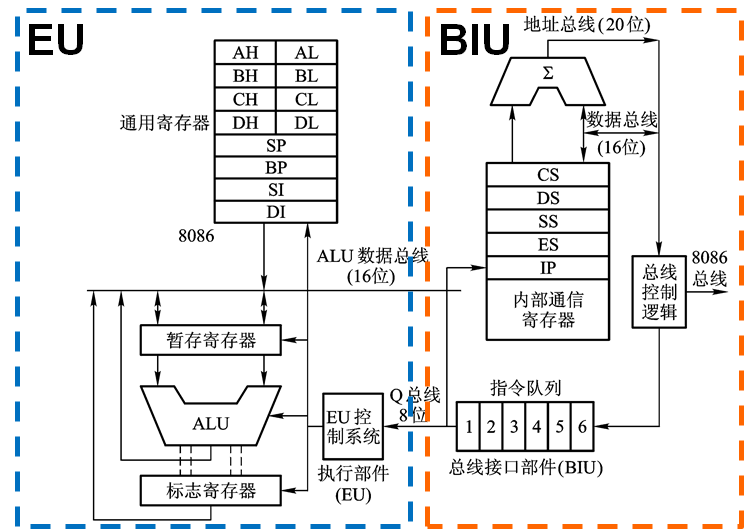

总线分类

地址总线:单向、三态总线

数据总线:双向、三态总线

控制总线:单向/双向、三态/非三态

电源和地线

备用线

每一次数据传输周期可以分为四个阶段:申请阶段、寻址阶段、传输阶段、结束阶段

T1:锁存地址

T2-T3:从存储器读数据到CPU

T4:恢复信号

Tw:T3周期的下降沿采用READY信号线,如果READY信号有效,则在T3状态结束之后进入T4状态,如果无效则插入Tw。Tw继续采用READY信号线,直至READY有效进入T4,否则继续插入Tw。

三态:高电平、低电平、高阻态 连接电源(+5V),最小组态;接地,最大组态

连接电源(+5V),最小组态;接地,最大组态

低电平有效**,有效时别的总线设备不能获得对系统总线的控制

低电平有效**,有效时别的总线设备不能获得对系统总线的控制 T1时,用作地址总线的低16位A15~A**0

T1时,用作地址总线的低16位A15~A**0

T1时**,用作地址总线的高4位A19~A16;在其余时刻,表示CPU状态信息

8086工作在最大组态下**的典型时序

地址重叠:**

部分译码时,有些地址线是空闲的。

取1、取0,都可以选中某片存储器芯片。

因此,同一片芯片,就有好几个地址范围。

那么,这一块芯片的几个地址范围,和另外一块芯片的几个地址范围,

就有可能,有一部分,是相同的。

8086芯片的寻址能力:

寻址内存的能力:1MB(20位地址码)

寻址端口的能力:64K个端口(16位地址码)

I/O寻址状态时高位地址线A16~A19默认为零即处于无效状态,采用A0~A15进行寻址;