这一段的内容和上一章紧密结合,主要是根据指令和数据通路设计

1)PC的输入生成逻辑GenNextPC一共有四选一部件

1>in0对应的顺序取指的PC(即PC+4)

2>in1对应PC加上保存下来的分支指令的offset

3>in2对应PC高位拼接上保存下来的直接跳转指令instrindex

4>in3对应通用寄存器读端口1的数据读入。

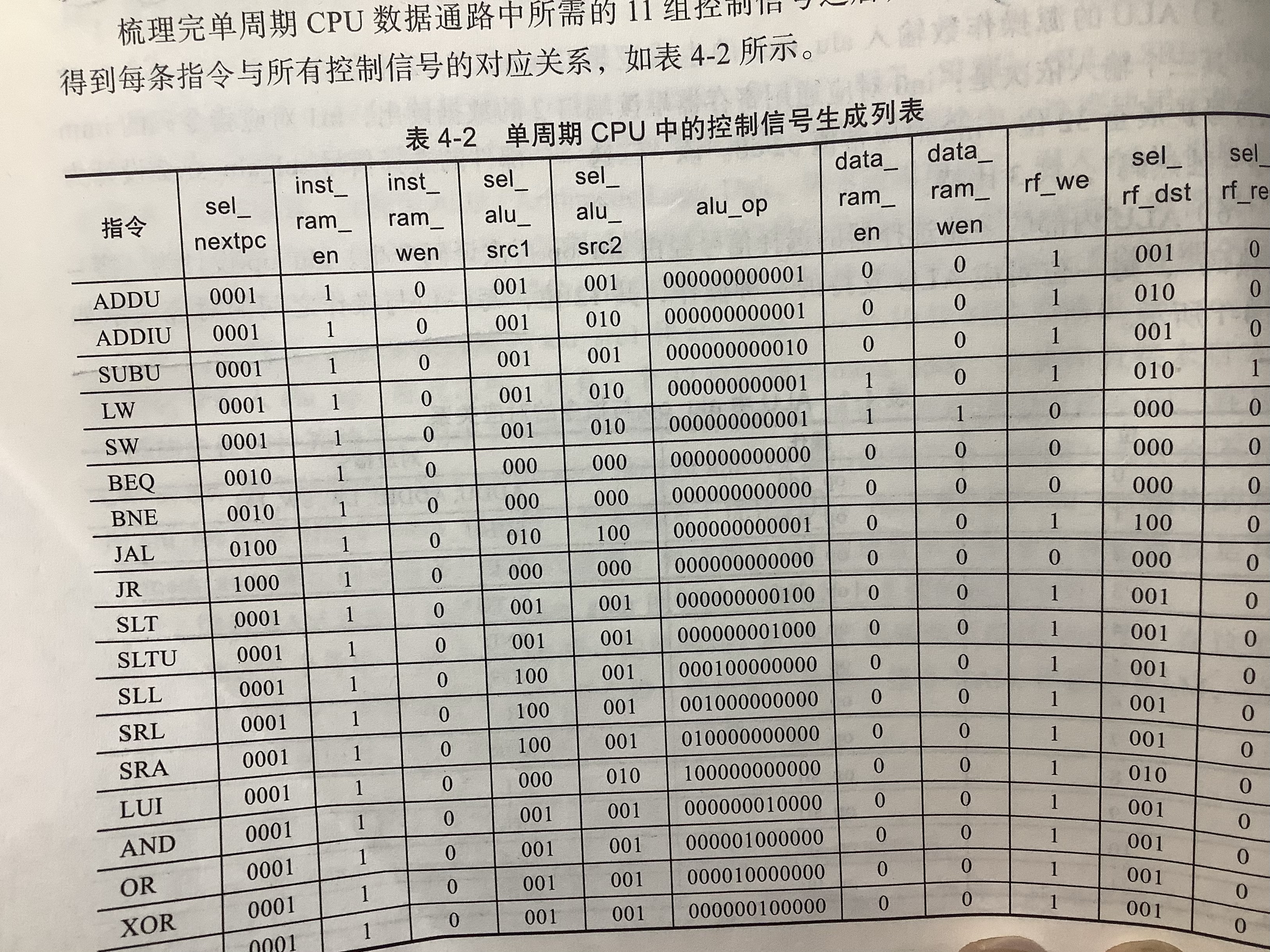

将该四选一的选自信号selnextpc设计为“零-独热码”信号宽4比特,每个比特对应一个数据输入 任何一个合法的选择信号只有一个比特设置为1.

2)对于指令RAM得我片选信号inst_inst_en高电平有效。对于现在的单周期CPU ,只要CPU的复位撤销,该信号就恒为1。

3)对于指令RAM的写使能信号inst_ram_en高电平有效。目前不考虑自修改代码之类的操作。所以RAM不会有来自RAM的写的请求。同时,指令RAM的内容初始化是由FPGA内部的电路自行加载完成的,不是通过外部设备写入的。所以inst_ram_wen信号恒为0。

4)ALU的源操作数输入的slu_src1的生成逻辑GenALUSrc1中包含一个三选一部件,三个输入依次是,

1)in0对应通用寄存器端读端口1的数据读出。

2)in1对应PC

3)in2对应指令码的sa域零扩展至32位。

该三选一的选择信号设计为“零-独热码”共3bit。

5)ALU的源操作数输入alu_src2的生成逻辑GenALUSrc2中包含一个“三选一”部件,器三个输入依次是:

1>in0对应的通用寄存器堆的读端口2的数据读出

2>in1对应指令码的imm域符号扩展至32位

该三选一部件的选择信号sel_alu_src1设计为“零-独热码”共3比特

6)ALU内部的多路选择器的选择经由alu_op再次译码产生,alu_op设计为“零-独热码”每一位ALU支持一种操作,共12位,每一位与操作之间的对应关系如表所示

ALU一种操作可能对应多种指令。通过将不同指令间的相同操作数提取出来,可以生成相同的ALU操作码。这样做使得设计ALU内部数据通路的控制信号时只关注ALU所实现的操作而不是指令。(?)可以降低设计的复杂度。

7)对于数据RAM的片选信号data_ran_en,高电平有效。与指令RAM类似,也将此信号恒置为1

8)对于RAM的写使能信号data_ram_wen,高电平有效

9)通用寄存器的写使能信号为rf_we

10)通用寄存器堆写地址生成逻辑GenRFRes中包含一个三选一部件,其三个输入依次为

1>in0对应的指令rd域,

2>in1对应指令的rt域,

3>in2对应的常值32’d31

该三选一的选择信号为sel_rf_dst设计为“零-独热码”共3bit

11)通用寄存器堆的写入生成逻辑GenRFRes包含一个“二选一”部件

1>in0对应ALU计算结果alu_res

2>in1对应从RAM中读出load操作的返回值ld_res该二选一部件的1bit选择信号sel_rf_res为0表示alu_res,为1表示ld_res.