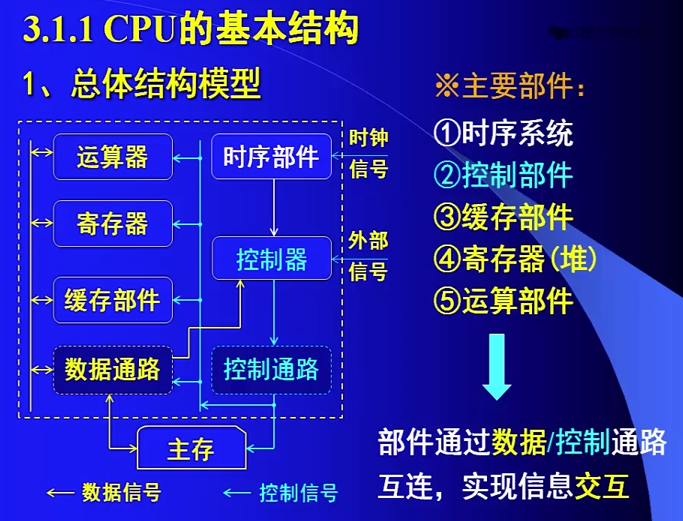

1、CPU概述

1)CPU的基本组成:

1、运算部件

2、寄存器组

3、微命令产生部件

4、时序系统

5、CPU内部数据通路结构

由CPU内总线将这些部件连接起来,实现部件之间的信息交换。

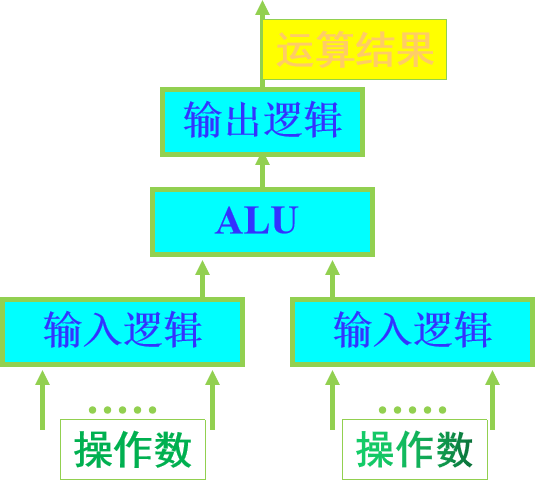

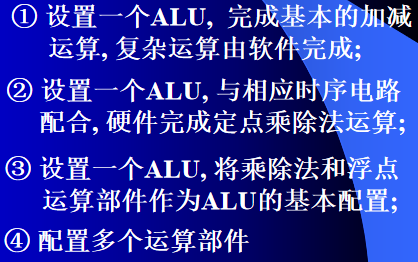

2、运算部件

1)任务:输入/直送,加工,输出

2)运算器构成

- 输入逻辑(选择器或暂存器)

- 算逻运算部件

3.输出逻辑(直送、移位、字节交换)

3、寄存器组

任务:存储各种用途的数据信息。

- 通用寄存器Ri,i可编程,一般成对出现

- 多个

- 通过地址码访问

- 提供操作数,地址码,存放运算结果

- 暂存器

- 多个,内部专用,无需分配地址码,不能在机器指令中使用

- 暂存产生的临时数据,以备后续操作使用

- ACC

- DR

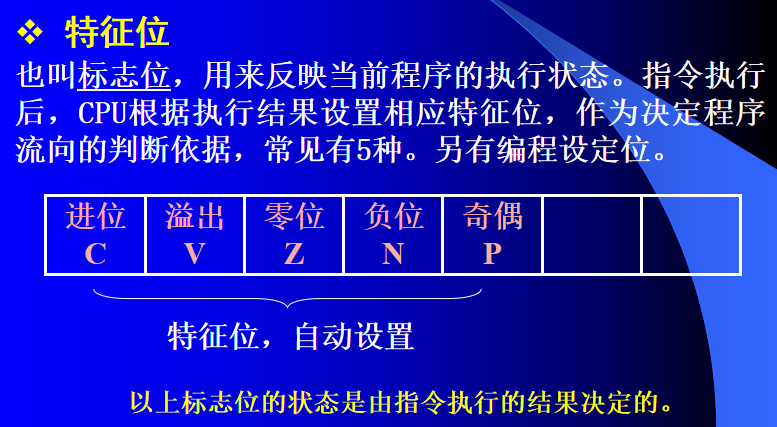

- FR

- 指令寄存器IR

- 只有一个,用于存放指令代码

- 程序计数器PC

- 仅一个

- 指示指令在存储器中存放位置

- 取址结束后,PC保存的地址自动修改

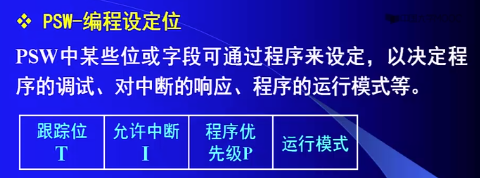

- 程序状态寄存器PSW,有两个空位(可编程)

- 仅一个

- 记录现行程序的运行状态和程序的工作模式。

- 地址寄存器MAR

- 只有一个

- 读写存储器时要定位存储单元,存放目标单元的地址码

- 先将有效地址送入MAR,再启动后续的读写操作

- 数据缓冲寄存器MBR

- 只有一个

- 过渡存放CPU与主存之间的交换的数据

- 无论是从主存读取的数据,还是写入主存的数据,都要经过MBR

- 堆栈指针SP

- 仅一个

- 固定存放堆栈的栈顶单元的地址码,根据这个地址码去读写堆栈

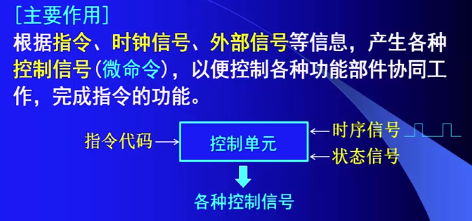

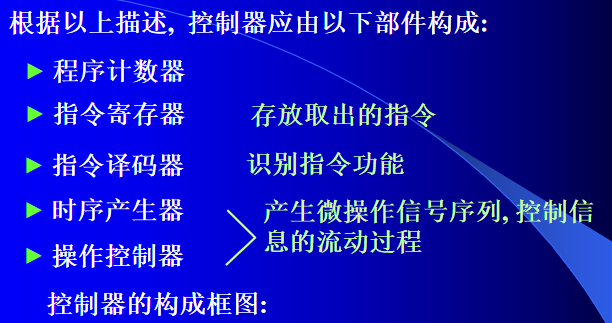

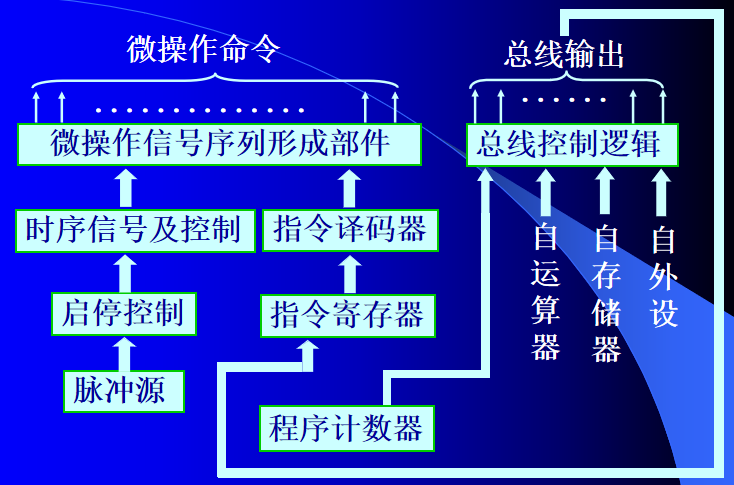

4、控制器

根据控制信息产生微命令序列,对指令功能所要求的数据传送进行控制,且在数据传送到运算部件时控制完成运算处理。

按产生微命令的方式,可以分为两类: 组合逻辑控制方式 微程序控制方式

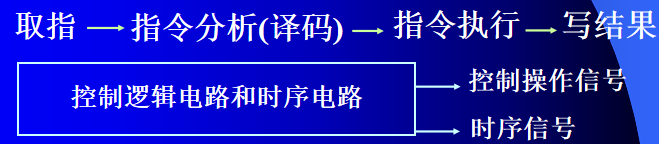

从指令执行的角度, 指令执行过程: 四个阶段:取址—指令分析(译码)—指令执行—写结果

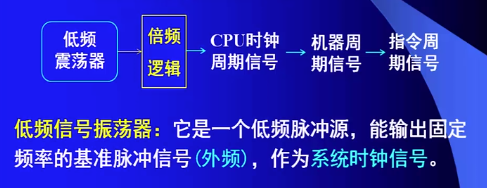

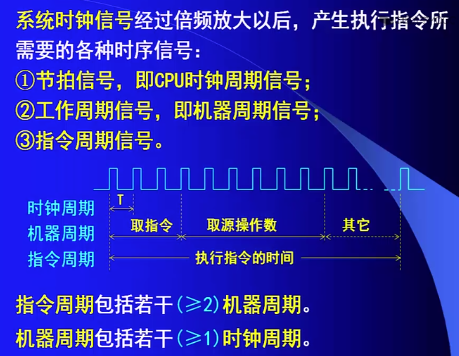

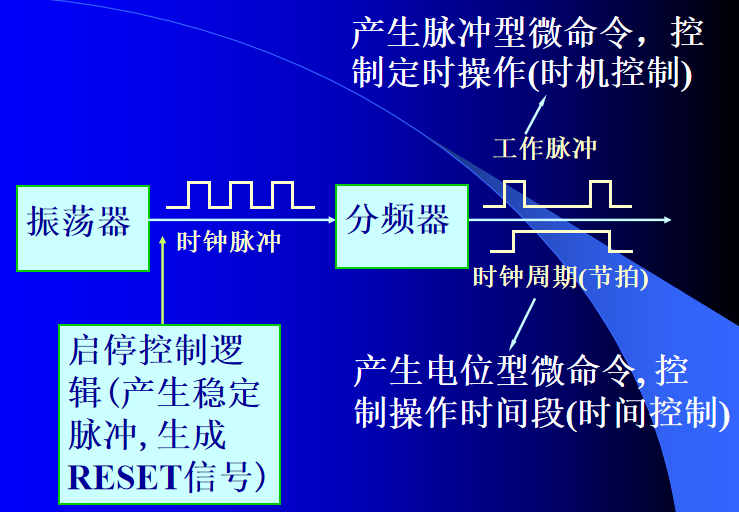

5、时序部件

- 时序信号

- 周期、节拍、脉冲等频率型信号序列

- 产生时序信号的部件则称为时序发生器或时序系统,由一个低频振荡器和倍频逻辑组成。

- 振荡器:一个脉冲源,输出频率稳定的主脉冲,也称为时钟脉冲,为CPU提供时钟基准。

- 时钟脉冲经过一系列计数分频,产生所需的节拍(时钟周期)信号或更长的工作周期(机器周期)信号。

时钟脉冲、时钟周期、节拍信号与有关控制条件相结合,产生所需的各种工作脉冲。

6、执行流程及控制

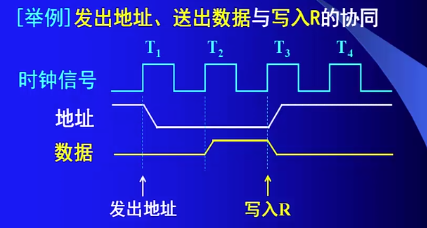

- 同步控制

- 每步操作都向统一的外部时序信号对齐

- 各步操作之间无交互

三个操作都靠外部时钟信号的驱动来实现协同

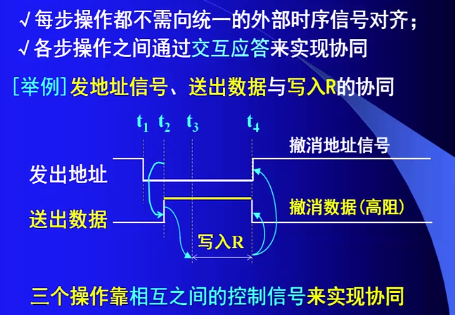

- 异步控制

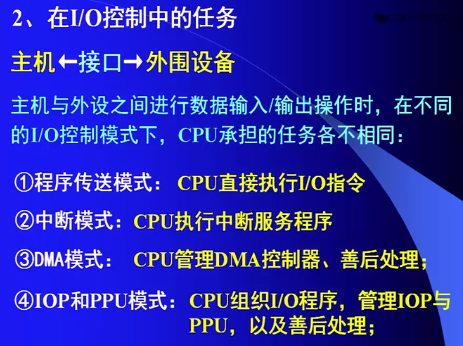

7、外部连接和IO任务

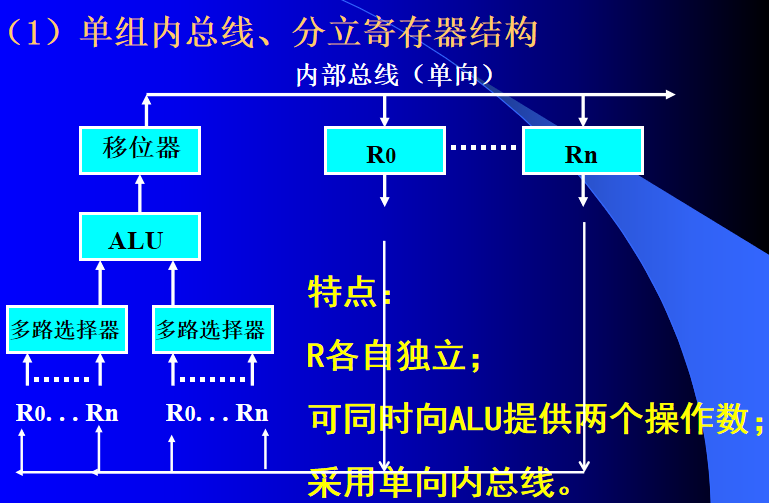

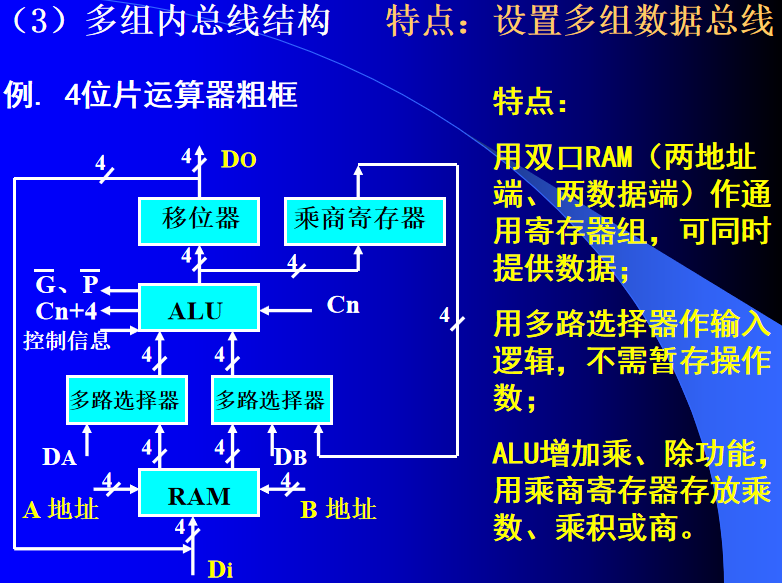

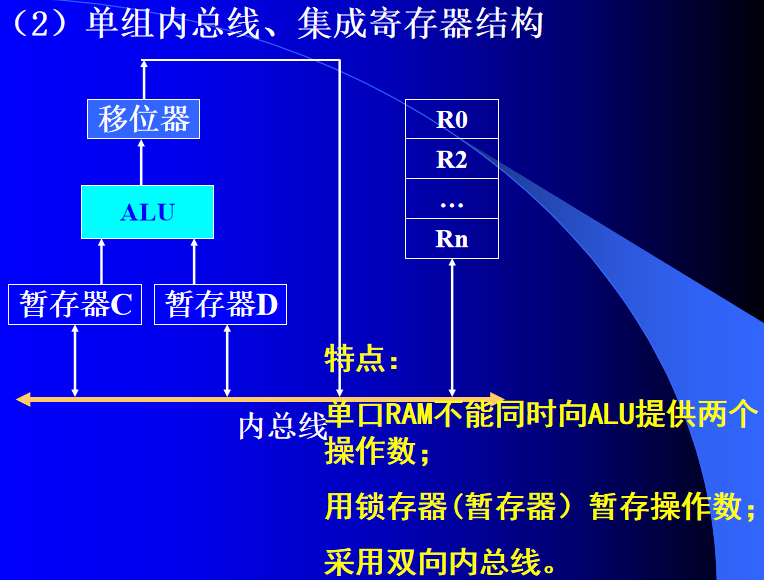

8、CPU内部的数据通路结构

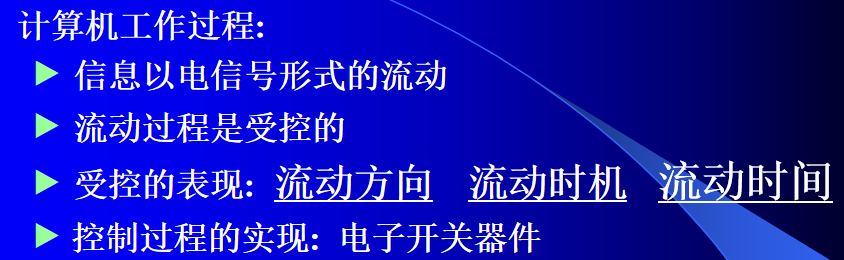

9、CPU工作原理

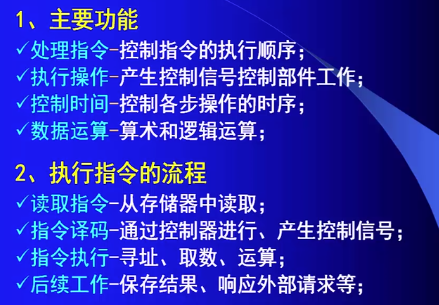

1)CPU主要功能

- 处理指令

- 执行操作

- 控制时间

- 处理数据

CPU工作过程

- 取指令

- 指令译码

- 指令执行

- 后续工作

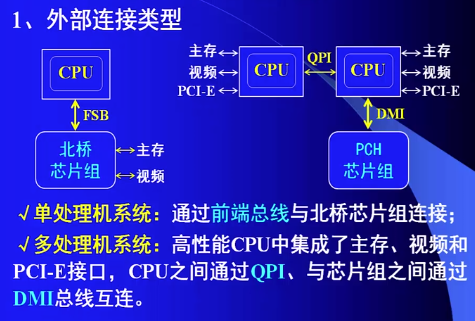

2)CPU外部连接

3)CPU控制信息传送的方式

- 程序输入输出方式

- 中断方式

- DMA方式

- 通道方式

4)其他

(1)CPU指令集:CISC、RISC

(2)CPU的发展:

- ①第1阶段,1946-1970(非微处理器) 特点:电子管和晶体管CPU阶段,体积大、功耗高、集成度低、运算速度慢。

- ②第2阶段,1971-1973(进入微处理器时代) 特点:中小规模集成电路,4位或8位微处理器。

- ③第3阶段,1974-1977:8位中高档微处理器。

- ④第4阶段,1978-1984:16位微处理器。

- ⑤第5阶段,1985-1992,32位微处理器。

- ⑥第6阶段,1993-2002,32位微处理器,工艺改进,指令集更丰富。

- ⑦第六阶段,2003-2004,64位单核。

- ⑧第七阶段,2005-现在,64位多核处理器为主。

10、指令系统

1、一般指令格式

2、常用寻址方式

3、面向用户指令类型

1)指令格式

(1)基本格式 op(操作码θ),A(地址码D)

(2)指令字长

- 定长指令格式——便于控制

- 变长指令格式——合理利用存储空间

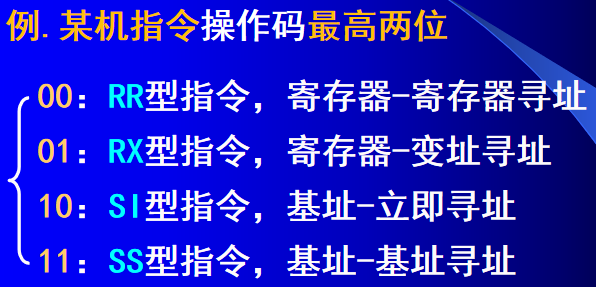

(3)操作码结构

- 定长操作码——各指令θ的位置、位数固定相同。

- 扩展操作码——各指令θ的位置、位数不固定,根据需要变化。(设置扩展标志)

- 复合型操作码——操作码分为几部分,每部分表示一种操作。

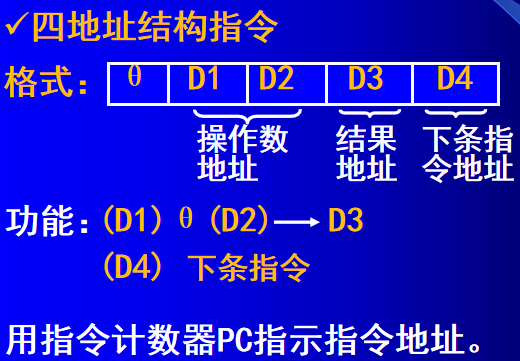

(4)地址结构

1》指令中提供的地址:存储单元地址码、寄存器编号

2》指令提供地址的方式:

- 显地址方式——指令中明显指明地址。

- 隐地址方式——地址隐含约定,不出现在指令中。

3》地址结构的简化:

三/二/一地址结构 (1)本身操作数少(2)缩略操作数

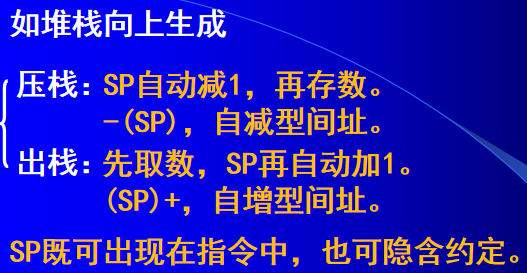

零地址结构 用于堆栈(位移)或特殊指令操作

2)常见寻址方式

寻址方式指寻找操作数地址或操作数的方式。

(1)常见寻址方式

1》立即寻址:指令直接给出操作数

- 定长格式:数在指令中,其长度固定、有限。

- 变长格式:数在基本指令之后,其长度可变。

用来提供常数、设置初值等。

2》直接寻址:指令直接给出操作数地址

- 存储单元号(数在M中) M指内存memory,D指主存地址

- 寄存器号(数在R中)

主存直接寻址(绝对寻址) S =(D)

- 定长格式:有效地址D的位数有限, 限制访存范围

- 变长格式:D的位数可覆盖 整个存储空间

寄存器直接寻址 S =(R)

- R所占位数少; 访问R比访问M快

3》间接寻址:指令给出操作数的间接地址

- 存储单元号(数在M中)

- 寄存器号(数在M中)

主存间接寻址 S =((D))

寄存器间接寻址 S =((R))

- R所占位数少;R可提供全字长地址码; 修改R内容比修改M内容快

堆栈间接寻址 S =((SP)),SP为堆栈指针

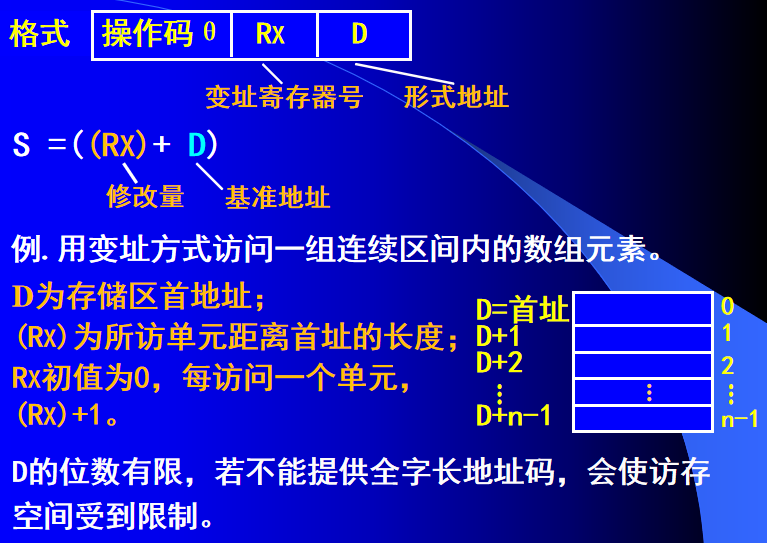

4》变址、基址寻址及其变化

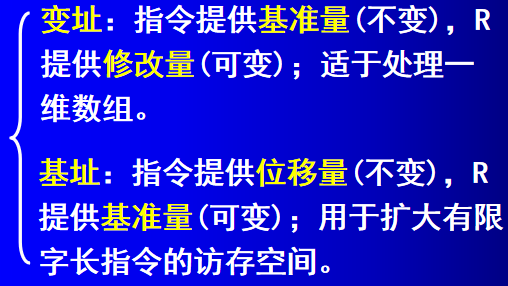

- 1>变址寻址:指令给出一个寄存器号和一个地址量,寄存器内容与地址量之和为有效地址。

- 便于访问一位数组

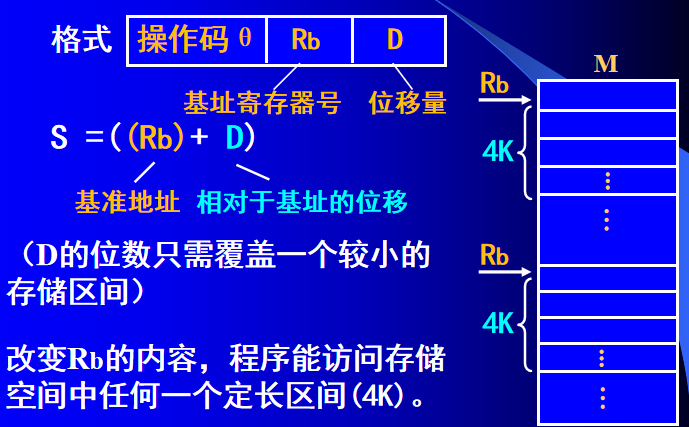

- 2>基址寻址:指令给出一个寄存器号和一个地址量,寄存器内容与地址量之和为有效地址。

- 便于访问二维数组中某类 指定的元素。

- 变址和基址的区别

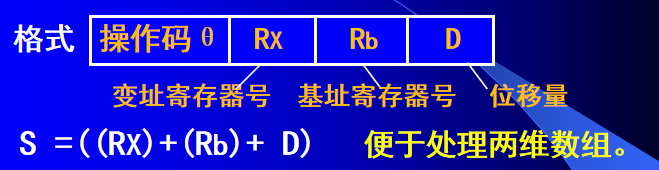

- 3>基址+变址:指令给出两个寄存器号和一个地址量,寄存器内容与地址量之和为有效地址。

- 4>相对寻址

- 5>页面寻址

(2)对寻址方式的补充说明

1》操作码隐含说明不同寻址方式

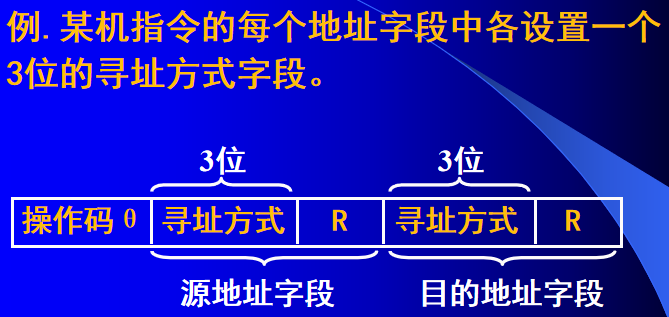

2》指令中设置专门字段说明寻址方式

3》指令的功能和类型

按指令功能分类:传送、访存、I/O、算数逻辑运算、程序控制、处理机控制等。

1>数据传输类指令

源地址对应的存储单元——(数据)——>目的地址对应的存储单元

这类指令主要用来实现主存和寄存器之间或寄存器和寄存器之间的数据传送

设计时需要考虑

- 规定传送范围/方向

- 指明传送单位:MOVB(8位)、MOVW(16位)、MOVL(32位)

- 设置寻址方式

2>输入/输出(I/O)指令

主机<——(各种信息)——>外设

设计时需要考虑

- I/O指令的功能扩展

- I/O指令中留有扩展余地:

- 指令中某些字段编码事先不定义,需要时再约定其含义。

- 用于外设种类、数量不多的场合。

- I/O接口中设置控制/状态寄存器

- 主机用输出指令或传送指令将具体设备的控制命令按约定的代码格式送往接口中的控制寄存器,向外设发出命令。

- 外设的状态信息也以某种格式放在接口的状态寄存器中,主机用输入指令或传送指令从状态寄存器中取出有关信息进行查询、分析。

- 如何设置控制/状态寄存器是接口设计的关键。

- 主机用输出指令或传送指令将具体设备的控制命令按约定的代码格式送往接口中的控制寄存器,向外设发出命令。

- I/O指令中留有扩展余地:

- 主机对外设的寻址方式:寻找I/O接口中的寄存器(I/O端口)的方式

- 外设单独编址

- 编址到寄存器:为每个寄存器(I/O端口)分配独 立的端口地址; I/O指令中给出端口地址。

- I/O地址空间不占主存空间,可与主存空间重叠。

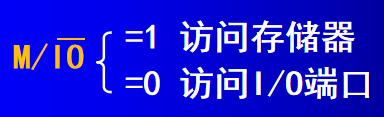

- 需设置标志区分访问对象,如

- 编址到寄存器:为每个寄存器(I/O端口)分配独 立的端口地址; I/O指令中给出端口地址。

- 外设统一编址

- 编址到寄存器:为每个寄存器(I/O端口)分配总线地址;访问外设时,指令中给出 总线地址。

- I/O端口占据部分主存空间。

- 常将存储空间的低端分配给主存单元,高端分配 给I/O端口,以示区分。

- 编址到寄存器:为每个寄存器(I/O端口)分配总线地址;访问外设时,指令中给出 总线地址。

- 外设单独编址

- I/O指令设置方式

- 设置专用I/O指令——>显式I/O指令

- 针对单独编址,用I/O指令访问I/O端口。

- 指令中说明输入/输出操作,并给出端口地址。

- 针对单独编址,用I/O指令访问I/O端口。

- 用传送指令实现I/O操作——>隐式I/O指令

- 针对统一编址,用访存指令访问I/O端口,不设专用的I/O指令。

- 通过I/O处理机进行I/O操作

- 设置专用I/O指令——>显式I/O指令

3>算术逻辑运算指令

4>程序控制指令:控制程序流程