零拷贝技术

参考链接

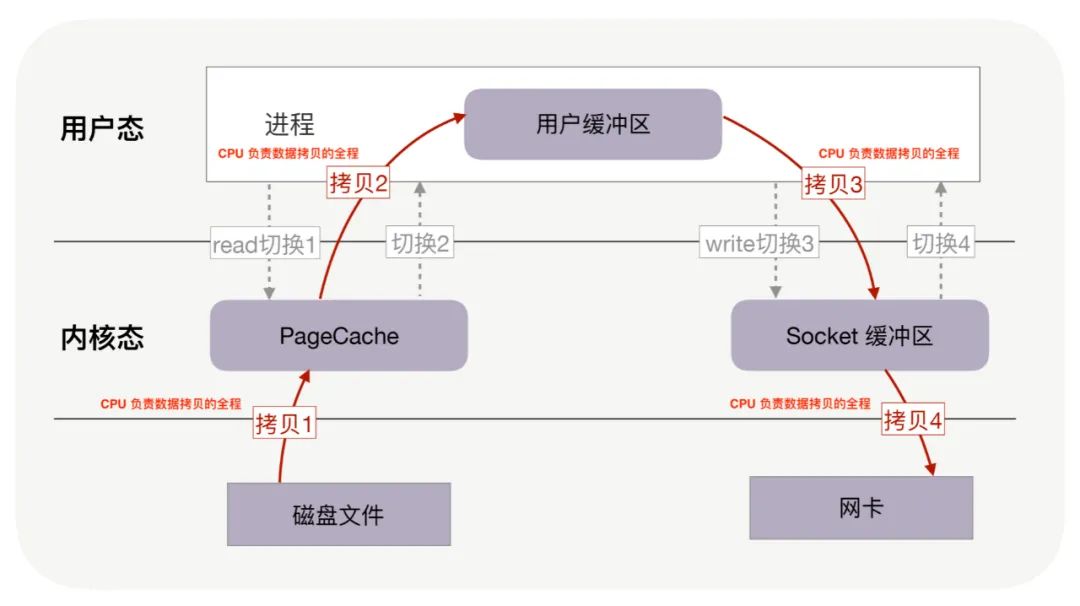

很多应用程序在面临客户端请求时,可以等价为如下系统调用,每次系统调用都需要进行线程上下文切换(用户态到内核态的转换)

- File.read(file, buf, len);

- Socket.send(socket, buf, len);

在没有任何优化技术使用的背景下,操作系统会为此进行4词数据拷贝和4次上下文切换

4次copy:

- CPU 负责将数据从磁盘搬运到内核空间的 Page Cache 中;

- CPU 负责将数据从内核空间的 Socket 缓冲区搬运到的网络中;

- CPU 负责将数据从内核空间的 Page Cache 搬运到用户空间的缓冲区;

CPU 负责将数据从用户空间的缓冲区搬运到内核空间的 Socket 缓冲区中;

4次上下文切换:

read 系统调用时:用户态切换到内核态;

- read 系统调用完毕:内核态切换回用户态;

- write 系统调用时:用户态切换到内核态;

- write 系统调用完毕:内核态切换回用户态;

会有如下问题:

- CPU 全程负责内存内的数据拷贝还可以接受,因为效率还算可以接受,但是如果要全程负责内存与磁盘、网络的数据拷贝,这将难以接受,因为磁盘、网卡的速度远小于内存,内存又远远小于 CPU;

- 4 次 copy 太多了,4 次上下文切换也太频繁了;

DMA 参与下的数据四次拷贝

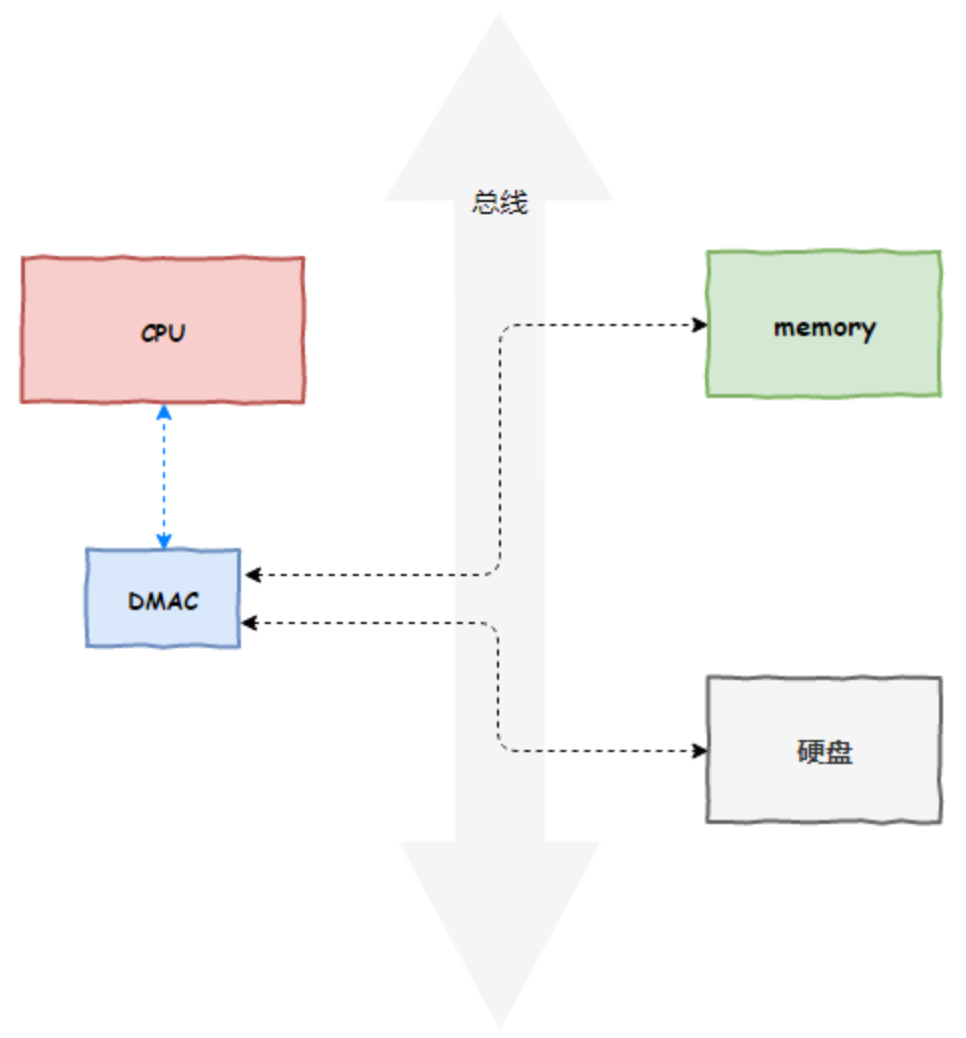

DMA 技术很容易理解,本质上,DMA 技术就是我们在主板上放一块独立的芯片。在进行内存和 I/O 设备的数据传输的时候,我们不再通过 CPU 来控制数据传输,而直接通过 DMA 控制器(DMA Controller,简称 DMAC)。这块芯片,我们可以认为它其实就是一个协处理器(Co-Processor)。

我们用千兆网卡或者硬盘传输大量数据的时候,如果都用 CPU 来搬运的话,肯定忙不过来,所以可以选择 DMAC。而当数据传输很慢的时候,DMAC 可以等数据到齐了,再发送信号,给到 CPU 去处理,而不是让 CPU 在那里忙等待。

在 DMAC 控制数据传输的过程中,我们还是需要 CPU 的进行控制,但是具体数据的拷贝不再由 CPU 来完成。

DMA 代替了 CPU 负责内存与磁盘以及内存与网卡之间的数据搬运,CPU 作为 DMA 的控制者,如下图所示:

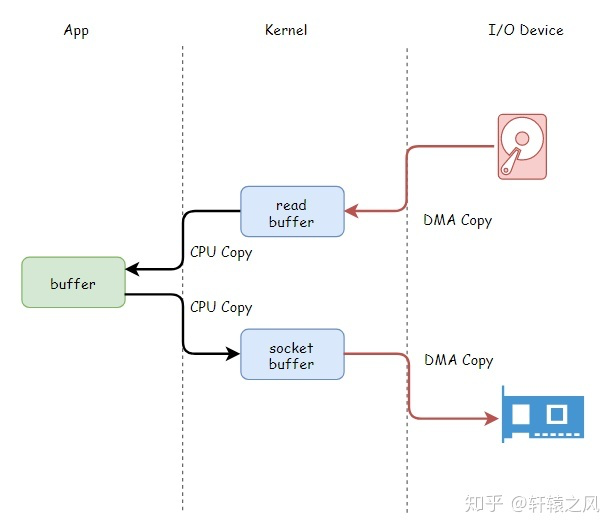

但是 DMA 有其局限性,DMA 仅仅能用于设备之间交换数据时进行数据拷贝,但是设备内部的数据拷贝还需要 CPU 进行,例如 CPU 需要负责内核空间数据与用户空间数据之间的拷贝(内存内部的拷贝)

上图中的 read buffer 也就是 page cache,socket buffer 也就是 Socket 缓冲区。 相当于把四次拷贝变成了两次拷贝