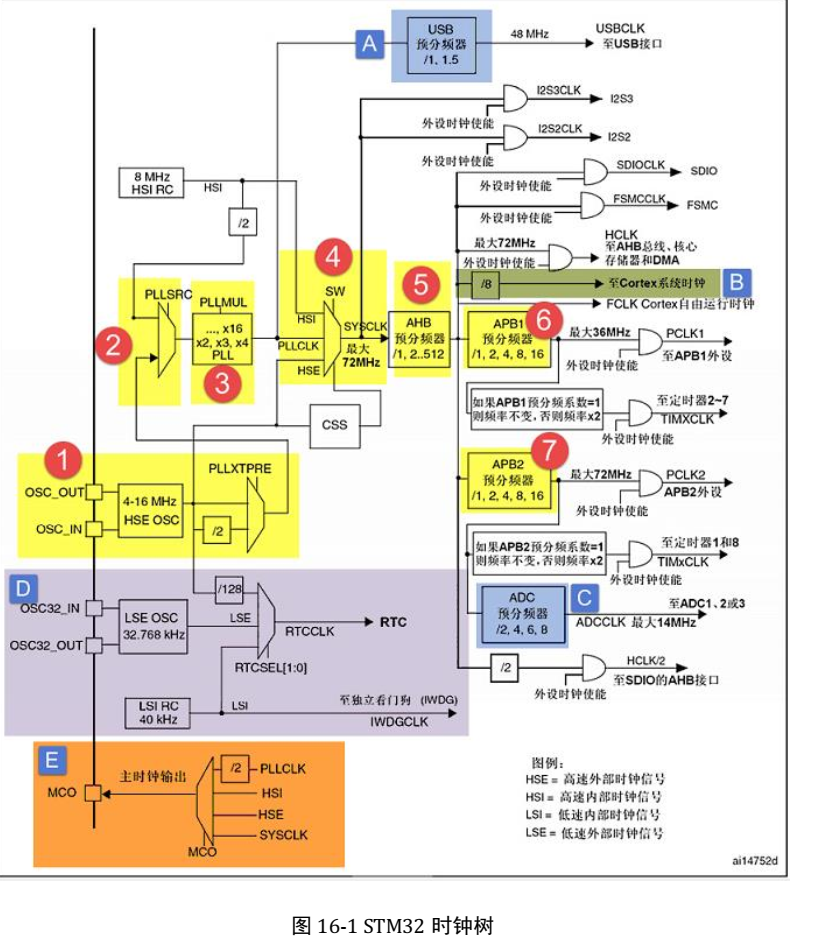

时钟是整个单片机的心脏,是“源”,没有时钟,单片机就是一具尸体,没办法工作。

一、系统时钟

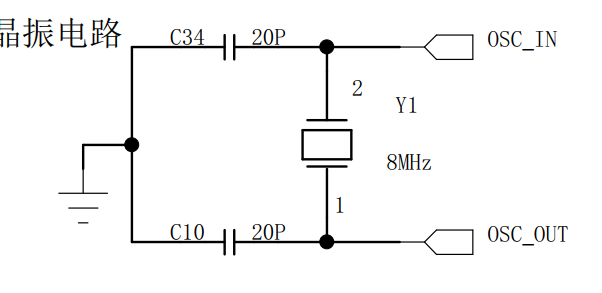

1、HSE高速外部时钟

由外部晶振产生,如果是有源晶振,则OSC_OUT要悬空,如果采用无源晶振,则需要配置谐振电容,如图20p法。最常用的无源晶振就是8MHz

2、HSI高速内部时钟

由芯片内部产生,不是外部提供的。STM32F103VET6提供的为8M大小,当HSE时钟故障了,系统时钟会自动切换到HSI时钟8M,单片机低速运行,基本属于瘫痪状态

3、锁相环时钟PLLCLK

由HSI/2、和HSE经过倍频得到,倍频系数从1到16。一般选用8M的HSE时钟,经过7倍频,得到72MHz锁相环时钟,锁相环时钟来作为系统时钟。如过选用HSI/2=4MHZ作为PLL时钟来源,则最大到4M×16=64MHZ,不满足ST公司推荐的STM32F103单片机的72MHZ时钟,单片机大部分功能在64MHZ还是能正常工作的。

4、系统时钟SYSCLK

虽然SYSCLK来源可以是HSI、HSE、PLLCLK,我们一般只选用PLLCLK作为系统时钟,72MHZ

二、外设时钟

5、AHB高速总线时钟HCLK

由系统时钟经过AHB预分频器得到,分频系数有:1,2,4…,512,最高为系统时钟72MHz,可以给挂载到AHB总线上的外设、核心存储器、DMA、Cortex系统时钟、FCLK提供时钟。

一般就先设置成72MHZ,等用到具体的外设时,再具体进行配置

6、APB2总线时钟PCLK2

由AHB总线时钟HCLK分频得到,一般分频系数设置为1,即72MHZ。用来给挂载到APB2高速总线上的外设提供时钟资源,例如GPIO、USART1等,具体的外设的时钟,等到用到该该外设时具体配置。还给高级定时器1和8提供72MHZ时钟

7、APB1总线时钟PCLK1

低速总线时钟,由AHB总线时钟HCLK分频得到,最高36MHZ,一般就是将分频系数设置为2,得到36MHZ,同样的给挂载到APB1低速总线上的外设提供时钟资源。同时也通过2倍频后(36×2MHZ)后给通用定时器2-7提供72MHZ时钟。

三、其他时钟

- USB时钟:由PLLCLK经过预分频器得到,分频系数有1,1.5….等,常用的USB时钟为48MHZ

- ADC时钟:模数转换时钟,最高限制在14MHZ,由高速总线APB2时钟进过分频器得到,分频系数有2,4,6,8,由于PCLK2最高72MHZ,经过这些分频系数时,达不到刚好的14MHZ,所以实际使用的时候,ADC时钟工作在小于14MHZ的情况下,如72/6=12MHZ。

- RTC时钟:由HSE时钟128分频、低速外部时钟LSE、低速内部时钟LSI提供(不稳定,频率受温度偏移比较大),常用LSE作为来源,为芯片内部的RTC外设提供时钟源

- 独立看门狗时钟:IWDGCLK,由LSI提供

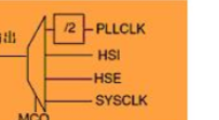

- MCO时钟:由

提供,是微控制器时钟,由PA8复用输出时钟

提供,是微控制器时钟,由PA8复用输出时钟