1.计算机系统概述

1.1计算机的发展史

- 第一阶段(1946-1956):电子管计算机特点:集成度低,体积大,功耗高,运行速度慢,操作复杂。

- 第二阶段(1956-1964):晶体管计算机特点:相对电子管就撒你,体积小,速度快,功耗低,可靠性高,配备显示器。

- 第三阶段(1964-1970):集成电路计算机特点:操作系统诞生。

- 第四阶段(1970-至今):超导规模集成电路特点:集成度高,速度快,体积小,价格低,用途广泛。

-

1.2计算机的分类

超级计算机、大型计算机、迷你计算机(普通服务器)、工作站、微型计算机(个人计算机)。

1.3计算机的体系与结构

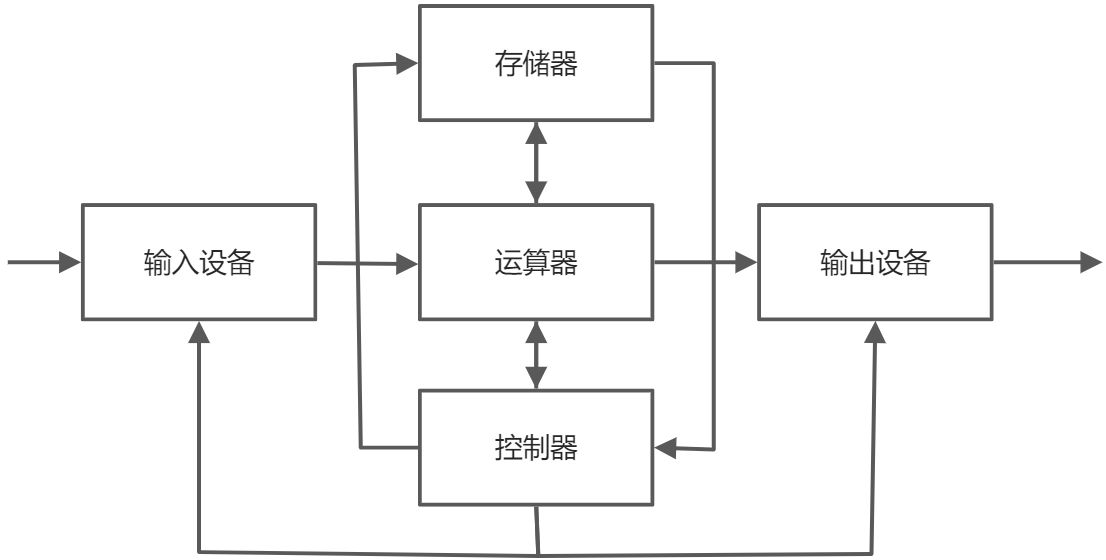

冯·诺伊曼体系:将指令和数据一起存储的计算机设计概念结构,由存储器、控制器、运算器、输入设备、输出设备五个部分。

- 现代计算机的结构:以存储器为核心,解决冯·诺伊曼体系瓶颈问题(CPU与存储设备之间的性能差异)。CPU=计算器+控制器+存储器。

1.4计算机系统的层次结构

从下到上依次为:微程序设计级、一般机器级、操作系统级、汇编语言级、高级语言级。

- 硬件

第一级:微程序机器层M0(微指令系统),由硬件直接执行微指令。

第二级:传统机器M1(机器语言机器),用微程序解释机器指令。

- 软件

第三级:虚拟机器M2(操作系统机器),用机器语言解释操作系统。

第四级:汇编语言M3(汇编语言机器级),用汇编程序翻译成机器语言程序。

第五级:虚拟机器M4(高级语言机器),用编译程序翻译成汇编语言程序

1.5计算机的主要性能指标

- 机器字长:CPU一次能处理的二进制数据的位数;

- 数据通路带宽:数据总线一次所能并行传送信息的位数;

- 主存容量:主存储器所能存储信息的最大容量;

- 运算速度:

- 按照存储介质:半导体存储器(内存、U盘、固态硬盘)、磁存储器(磁带、磁盘)

按照存取方式:随机存取RAM(随机读取,与位置无关)、串行存储器(按顺序查找,与位置有关)、只读存储器(只读不写)

3.2存储器的层次结构

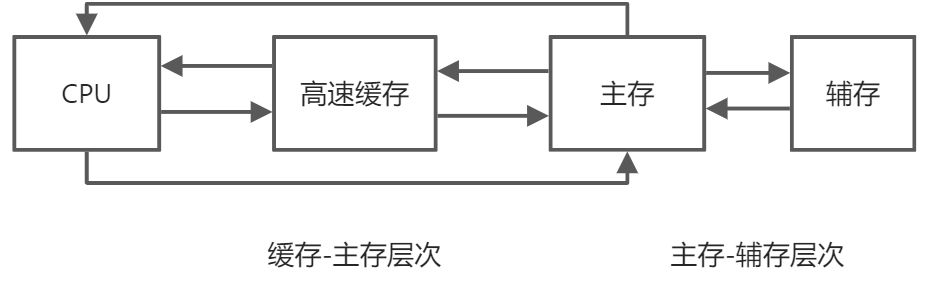

缓存-主存层次:局部性原理,在CPU与主存之间增加一层速度快容量小的Cache,解决主存速度不足的问题。

- 主存-辅存层次:局部性原理,主存之外增加辅助存储器,解决主存容量不足的问题。

- 局部性原理:是指CPU访问存储器时无论时存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中。

3.3计算机的主存储器

- 主存储器包括:随机存储器RAM(静态RAM和动态RAM)、只读存储器等。

- 主要技术指标:存储容量、存取速度和存储带宽。

主存储器相关算法:

工作原理:命中率是衡量缓存的重要性能指标,理论上CPU每次都能从高速缓存取数据的时候命中率为1.

- 高速缓存的替换时间:当缓存没有数据,需要从主存载入数据的时候。

- 高速缓存的替换册率:随机算法、FIFO、最不常使用算法LFU、最近最少使用算法LRU。

高速缓存的计算:

命中率:(Nc:访问Cache的总命中次数,Nm:访问主存的总次数(不命中次数))

Cache-主存系统的平均访问时间:(tc命中时的Cache访问时间,tm未命中时的主存访问时间)

访问效率:

4.指令系统

-

5.中央处理器

6.总线与IO系统

6.1总线

概述:计算机系统中的各部件之间进行信息传输的公共通道。(即多个部件共享传输部件)

- 作用:解决不同设备之间的通信问题。

- 特点:某一时刻只能由一路信息在总线上传输,即:分时使用。

- 分类:片内总线(高集成度内部的信息传输线)、系统总线(细分为数据总线、地址总线、控制总线,是CPU、主存、IO设备、各组件之间的信息传输线)

- 总线的仲裁:目的是解决总线使用权的冲突问题。包括三种方法:链式查询、计时器定时查询、独立请求

| | 链式查询 | 定时器定时查询 | 独立请求 |

| —- | —- | —- | —- |

| 控制线数 | 3

总线忙:1、总线请求:1、总线同意:1 | ⌈log2n⌋+2

总线忙:1、总线请求:1、总线同意:⌈log2n⌋ | 2n+1

总线忙:1、总线请求:n、总线同意:n | | 优点 | 优先级固定、结构简单、容易扩充设备 | 优先级灵活(介于两者之间) | 相应速度快、优先级次序灵活 | | 缺点 | 对电路故障不敏感、优先级不灵活(优先级低的设备难以获得请求) | 对电路故障敏感介于两者之间,控制线路多,控制复杂 | 控制线路多,控制复杂 |

6.2常见的IO设备

- 字符输入设备:键盘;

- 图形输入设备:鼠标、数位板、扫描仪;

-

6.3输入输出接口的通用设计

数据线:I/O设备与主机进行数据交换的传送线(单向&双向);

- 状态线:I/O设备状态向主机报告的信号线;

- 命令线:CPU向I/O设备发送命令(读写信号、启动停止信号)的信号线;

-

6.4CPU与I/O设备的通信

程序中断:提供低速设备通知COU的一种异步方式,CPU可以在高速运转的同时兼顾低速设备的响应;

- 直接存储器访问(DMA):在主存和I/O设备之间建立独立的总线连接。DMA和主存交换数据时,通常采取停止CPU访问主存、周期挪用(窃取)、DMA和CPU交替的三种方式,解决争用主存冲突的问题。

常见问题:

同步通信和异步通信辨析:

(1)同步通信:由统一的时钟控制,控制方式简单,灵活性差,当系统中的各部件工作速度差异大的时候,总线工作效率明显下降,适用于差别不大的场合。

(2)异步通信,指没有统一时钟控制的通信,部件之间采用应答方式进行联系,控制方式较同步方式,灵活性高,当系统中各部件工作速度差异大的时候,由利于提高总线工作效率。