RSIC-V——指令集 spec 阅读笔记——向量扩展 0.9

KGback 2020-11-09 13:52:57

1332

收藏 9

分类专栏: RISCV

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_39815222/article/details/109570539

版权

RISCV 专栏收录该内容

5 篇文章 1 订阅

已订阅

1. V 扩展简介

- 基本

- 矢量指令进行优化的硬件可以应用到图像处理、 AI 或机器学习中

- RVV 矢量长度可变

- RVV 较为考验软件部分,要求编译器能够优化代码执行向量指令

- V 扩展中容易混的几个参数

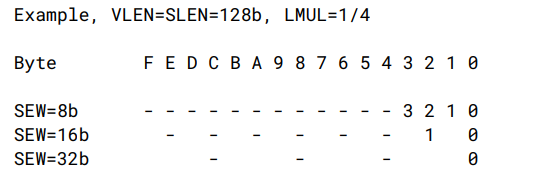

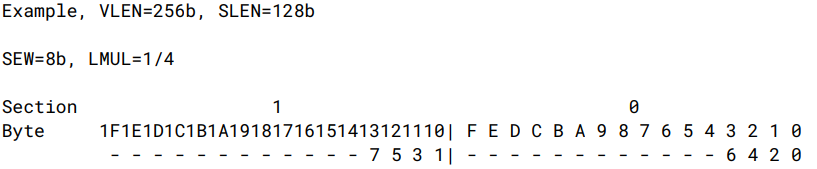

- VLEN:向量寄存器宽度,要求VLEN ≥ ELEN

- ELEN:单个向量元素的最大宽度,要求 ELEN ≥ 8,并且必须为 2 的幂。一般的,元素宽度的最大值就是 XLEN 值。

- SLEN:分段距离,VLEN ≥ SLEN ≥ 32,并且必须为 2 的幂。SLEN 表示的是在相同的元素级混合宽度算术运算操作中的向量寄存器 bit 位之间的最大位移

(该量在 rvv1.0 版本中已删去)

- SEW:standard element width 标准元素宽度,向量寄存器被视为分成 VLEN / SEW 个标准宽度元素。

- LMUL:每组向量寄存器中向量寄存器个数, 需满足LMUL≥SEW / ELEN,即在极限情况下(VLEN=ELEN),要使得 LMUL*VLEN>=SEW,一个寄存器群要能保存一个计算元素。

- VLMAX:可以使用单个向量指令操作的最大元素个数,等于 VLEN/SEW*LMUL

- AVL:外部要求的参与运算的元素个数

- vl:向量长度寄存器,保存要通过向量指令更新的元素数,vl 的值为 min(VLMAX, AVL)

- 32-bit/64-bit 区别

32 位机和 64 位机本质上没有区别,因为向量运算中基本的元素宽度 SEW 是可配置的。

唯一的区别在于特权寄存器的配置

2. V 扩展中的寄存器

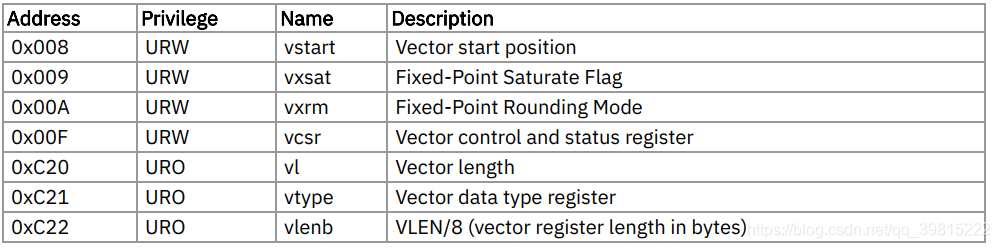

riscv-v-spec 规定在基本 spec 增加了 32 个向量寄存器(记为 v0-v31,位宽均为 VLEN)和 7 个非特权 CSRs(分别为vstart, vxsat, vxrm, vcsr, vl, vtype, vlenb,位宽均为 XLEN)

1. 与特权寄存器相关配置

- mstatus[10:9]

向量上下文状态字段 VS:mstatus[10:9](同样包括 sstatus[10:9])。VS 的定义类似于浮点上下文状态 FS。

当 VS 字段被设置为 Off ,试图执行任何向量指令或访问向量 CSRs 时,会引发非法指令异常;当被设置为 Initial 或 Clean ,执行更改向量状态的指令,包括向量 CSRs 指令,该字段会变为 Dirty 。

2. 普通向量寄存器

v0 寄存器一般作为掩码寄存器,其他寄存器均作为普通向量寄存器使用

3. 特殊向量寄存器

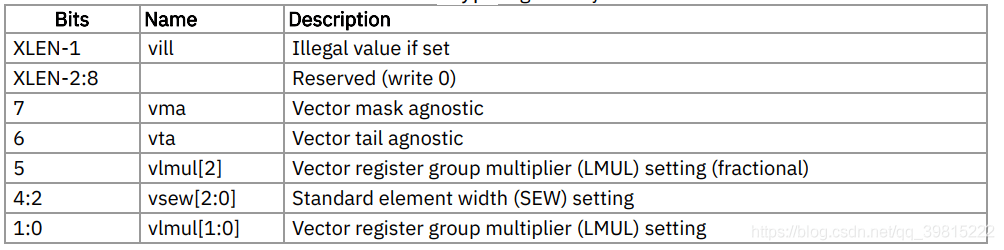

- vtype: 向量类型寄存器

用于解释向量寄存器文件内容的默认类型,并且只能通过 vsetvl 指令进行更新。向量类型还决定了每个向量寄存器中元素的排布,以及如何对多个向量寄存器进行分组。

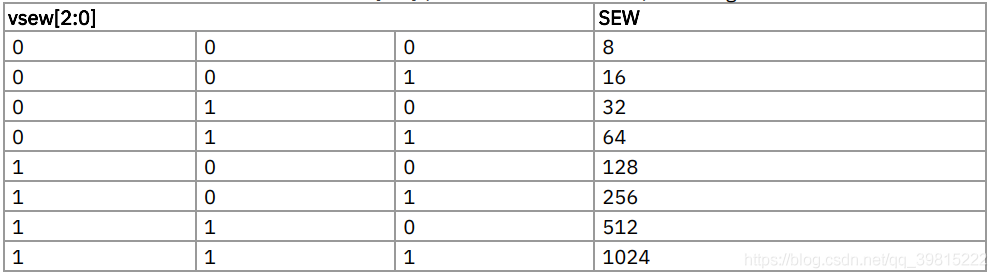

- vsew[2:0]:设置向量寄存器中每个元素宽度 SEW,向量寄存器被视为分成 VLEN / SEW 个标准宽度元素。

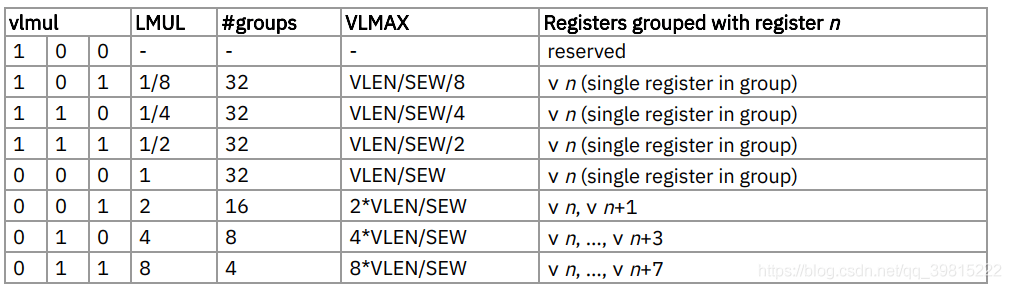

- vlmul[2:0]:向量寄存器分组,多个向量寄存器可以分成一组,以便单个向量指令可以对多个向量寄存器进行操作,

LMUL = 2^(vlmul[2:0]) VLMAX=LMUL*VLEN/SEW

注意:vlmul[2:0]是一个有符号数

寄存器组可以对相同向量宽度的标准宽度元素的溢出进行有效处理,即是动态修改 vtype 值,保证 SEW/LMUL 为常量即可

注意:在某些混合 LMUL 配置的指令中,向量寄存器的编号均采用 LMUL 最大值的配置 - vill: 向量类型非法,若 vill 置 1,则依赖于 vtype 的指令会引发非法指令异常,且其余的 XLEN-1 的所有值均被强制置 0

- vma:

- vl: 向量元素长度寄存器

该寄存器的值是通过 vsetvli / vsetvl 两个指令自动设置的,

即选取 VLMAX= VLEN/SEM*LMUL 和 AVL(需要被应用的向量寄存器长度,通常通过一个 GPR 传递)中的较小值,给 vl 寄存器,并将该值通过一个 GPR 保存起来

vl=min(VLMAX, AVL)

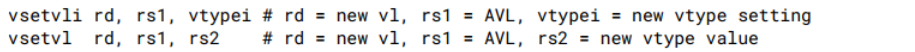

通常用指令 vsetvli 设置 vtype 值,用 vsetvl 作为上下文保存

- vlenb: 向量寄存器长度(以字节为单位)

该值为一个定值(VLEN/8),方便代码知道 VLEN 的值

注意 vlenb 和 vl 代表的意义没有直接关系,不要混淆。

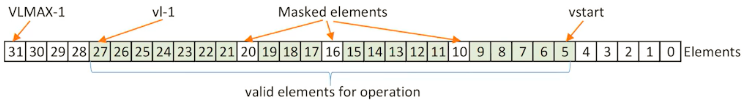

- vstart: 向量起始索引寄存器

指定向量指令要执行的第一个元素的索引。该寄存器只有在向量指令陷入时才被硬件写入,表示在其上执行陷入指令的元素(同步异常或异步中断),并且在处理可恢复陷入指令返回后,向量操作应从 vstart 指向的元素开始执行,指令执行结束后 reset vstart 值。

所有向量指令都定义为从 vstart 中给定的元素编号开始执行,并在执行结束时将 vstart 置 0。

使用 vsetvl 指令配置时,如果 vstart 寄存器中的值大于向量长度 vl 时,则不执行任何元素操作,然后 vstart 寄存器被重置为零。

vstart、掩码、VL 设置对应的元素运算范围如上图所示。

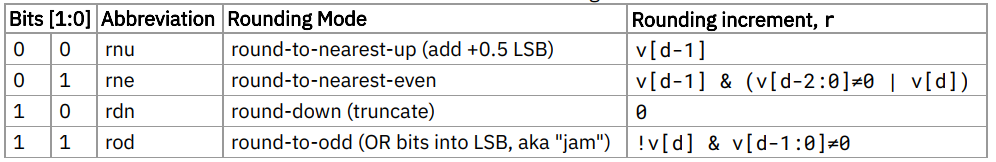

- vxrm: 向量定点舍入模式寄存器

定点舍入算法如下: 假设预舍入结果为 v,d位结果被舍入。然后,舍入结果为(v>> d) + r,其中r取决于下表中指定的舍入模式

- vxsat: 向量定点饱和标志

保存一个读写位,表示定点指令是否必须使输出值饱和,以此适应目标格式。

- vcsr

vxrm 和 vxsat 可以通过单独 csr 指令来操作,也可以通过向量控制和状态寄存器 vcsr 来访问。

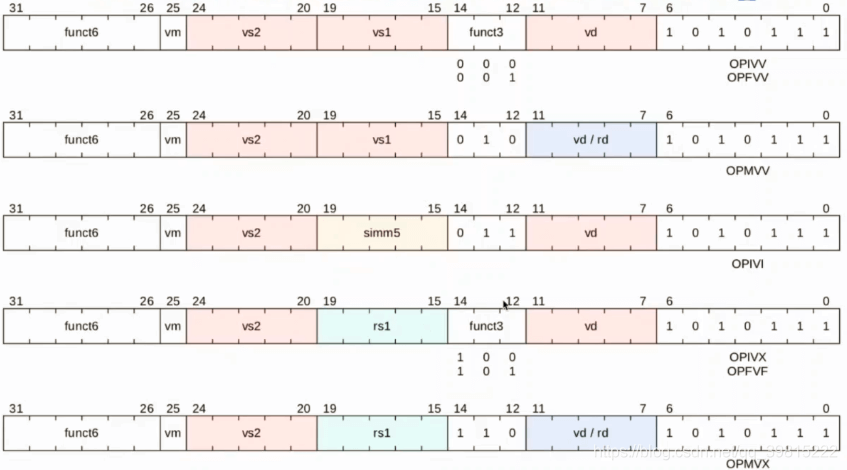

3. 指令编码格式

整数指令的编码格式

- 立即数若无特殊规定,均为有符号数

4. 指令功能

向量指令包括基本向量指令(必须实现的)和一些扩展指令(Z 开头、AMO)。

1. 配置指令

- vsetvli / vsetvl

该指令用来配置 vtype 和 vl 两个寄存器的值,并将 vl 的新值写入到 rd 寄存器中。

rs1 储存需要处理的向量大小(外部提出的需求),即 AVL(application vector length),该指令会将 AVL 与 VLMAX 作比较后取较小值赋给 vl,并赋值给 rd。这样做的目的是一方面如果 AVL>VLMAX,用来处理的向量元素不超过 SEW,另一方面使用尽可能少的资源处理数据

vsetvli 采用立即数赋值,vsetvl 用寄存器赋值

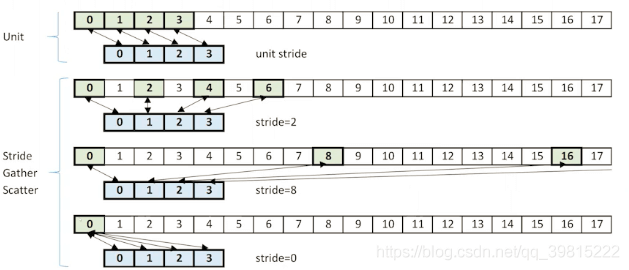

2 访存指令

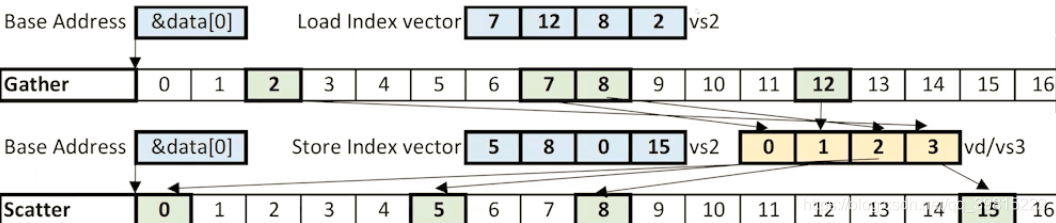

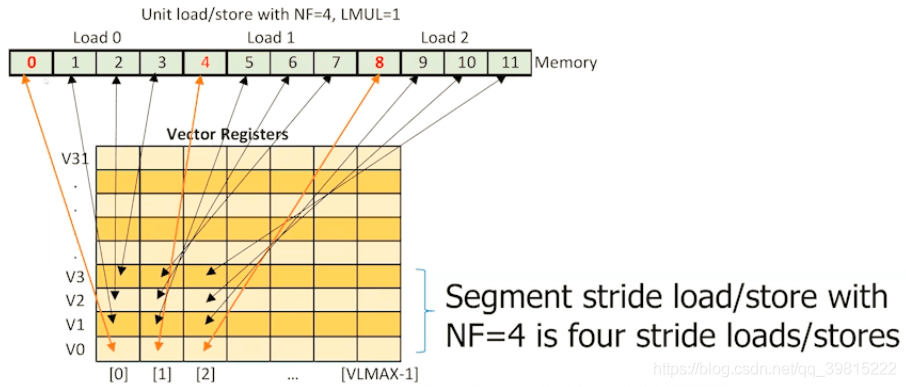

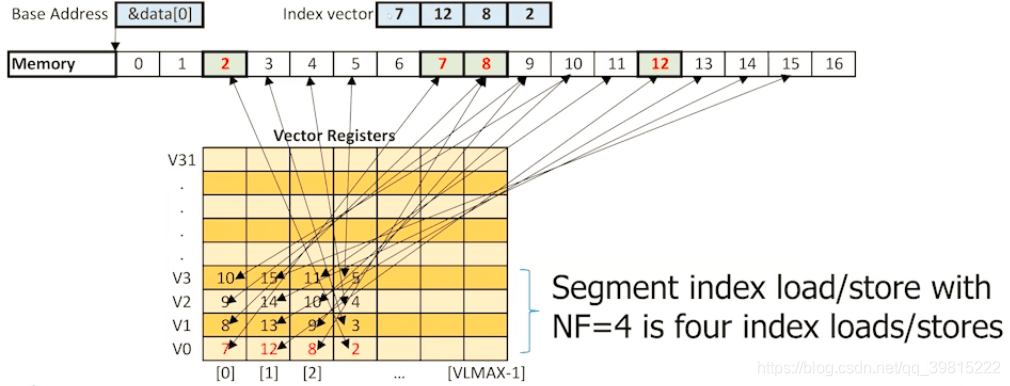

- stride/gather/scatter/segment 操作的区别

5. 补充:RVV 软硬件生态、

- 工具链

- 工具链对 intrinsic 的支持情况

EPI、SiPearl 和 SiFive 联合发布了一份 RISC-V “V”(向量) 扩展的 Intrinsics 的规范,并且已经被 RISC-V 采纳为标准规范。GCC 工具链已经较完整支持了 RISC-V “V” 向量扩展的汇编,并且持续在跟进向量扩展的最新版本 - 相关工具链

卡姆派勒开源 32bit LLVM 向量编译器:https://www.sohu.com/a/415960738_120163133

卡姆派乐信息科技有限公司此次开源的 RISC-V 向量编译器符合 riscv-v-spec-0.8 规范,支持的指令集架构为 isa=rv32imafcv,向量长度 vlen=128,共提供 6000 多个 intrinsic 函数接口。用户可以访问https://github.com/compiler-dev/llvm-rv.git 下载源码,并根据 README.md 说明,选择从源码编译运行环境所需要的 ld、newlib 和 libgcc 等工具集,也可以直接下载我们编译好的二进制包。二进制包下载地址:https://github.com/compiler-dev/rvvtool-chain-binaries,用户将编译好的开源 llvm 代码安装到这个路径即可使用。

开源代码中提供了每条 intrinsic 的接口说明,用户可以访问帮助文件查看每个接口的功能及参数。在目录 rvv-test/intrinsic 提供了 1500 多个测试文件(只包含 m1)。同时 rvv-test 目录下还提供了多个可以在 spike 模拟器上运行的测试用例。

LLVM 编译器 github 链接:https://github.com/compiler-dev/llvm-rv

编译后的可执行文件:https://github.com/compiler-dev/rvvtool-chain-binaries - 优化编译的支持情况

TSVC 博客:https://zhuanlan.zhihu.com/p/377577892

TSVC 测试:https://dl.acm.org/doi/fullHtml/10.1145/335684 - opencv 支持情况

参考链接:https://zhuanlan.zhihu.com/p/291207654?utm_source=wechat_timeline&utm_medium=social&s_r=0

- 目前实现 rvv 扩展的 CPU

玄铁 C910: rvv-0.7.1

晶心科技 NX27V:http://m.elecfans.com/article/1149316.html

https://blog.csdn.net/qq_39815222/article/details/109570539