lab3-cache

MUL DIV DIVU REM REMU MULW DIVW DIVUW REMW REMUW

补位是自动进行的吗…?所以用32位更快?

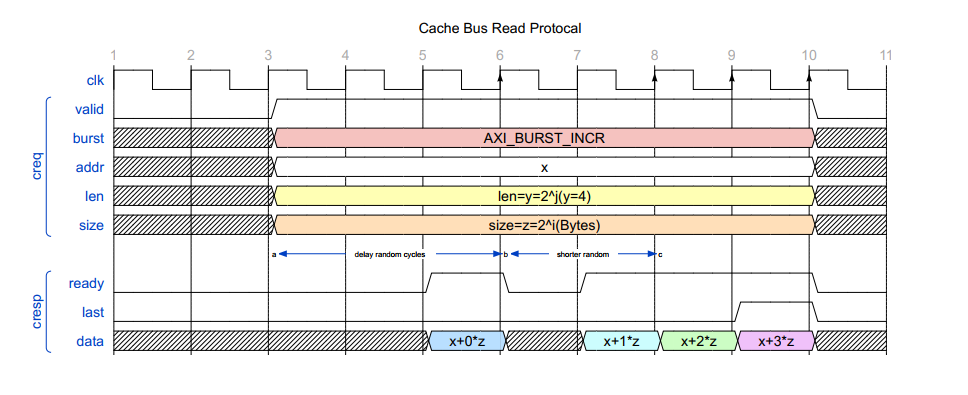

cache

从pipeline出发,连接到cache,dbus

我觉得吧,不需要知道那个iresp就是直接读memory,我现在加个cache

ireq是imem的需求,

-

认真听课:软工、计组 - 看完京剧剧目,简单记录

- 完成软工lab3的修改

- 学习离散数学并完成作业

- 洗衣服

- 洗澡

(道不同,不相为谋)

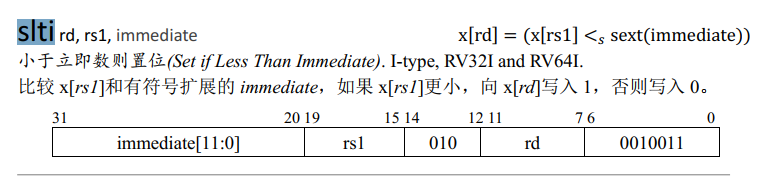

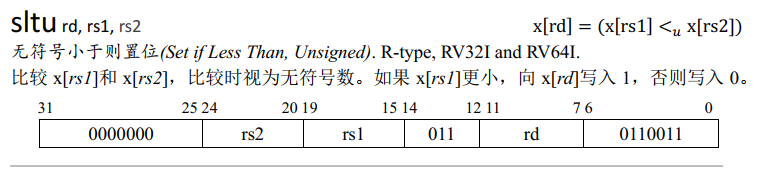

BNE BLT BGE BLTU BGEU SLTI SLTIU SLLI SRLI SRAI SLL SLT SLTU SRL SRA ADDIW SLLIW SRLIW SRAIW ADDW SUBW SLLW SRLW SRAW

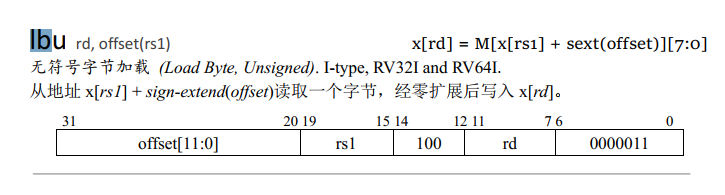

LB LH LW LBU LHU LWU SB SH SW

dresp是我的输出

is asserted

为什么在idle的时候需要存dreq?不理解…

ready 表示确定数据在cache中,so…

好的,所以读数据只读一个associativity里面的。

TODO:17:49

ready 时 数据写回cache

装填好一个line的data,控制strobe,写到对应的ass

dataBlock,输出一个line,输入一个line,data,offset,strobe

hit read write done

休息时间过长&&方式错误

不过没关系。

unhit read:fetch 有空位 done,无空位:替换1

解决fetch填装line_data的问题,另开一个变量存一个line的data,在fetch结束后将这个line写入cache同时写meta,这是在init完成的。如何区分

在确定hit时 需要存一个空位,

写入哪个asso?存入之前存的空位,整个写回两个ram。完成之后 直接传输这段到dresp。

读取数据:每次一个word,写入数据,每次一个byte,只要多分配index就行。index就是index*words_per_line+offset

还有一个问题,需不需要把 associativity分开来?感觉他们是联在一起的…

分析:将需要修改的地方列出来,保持平稳的心态。

知道什么叫:只需要管理地址吗?

如果mata每次读一个line会怎么样?

好像也不会怎么样emmm