1.1 CPU主板布局

总线概论

在很久之前是没有USB总线的,那个时候每个外设各自采用自己的接口标准,比如:鼠标生产厂商采用鼠标特有的接口,键盘生产厂商用键盘特有的接口,这样一来的话,PC机上就必须提供很多接口,这样一来增加了硬件设计难度和成本,直到后来USB接口的出现,它统一了很多外设接口的标准,不仅使得用户可以很方便地连接一些外设,更增强了PC的可扩展性。所以现在大家看到的鼠标、键盘、U盘、打印机等等这些外设都可以直接通过USB接口直接插到电脑上的。

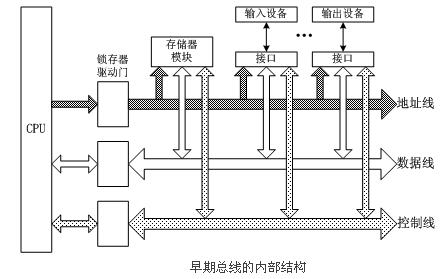

三总线结构

三总线结构,即:数据总线、地址总线、控制总线。它们分别用来传输不同类型的数据,数据总线用来传输数据,地址总线用来传输地址,控制总线用来传输一些控制信号

- 地址总线的宽度决定了

CPU的寻址能力- 数据总线的宽度决定了

CPU与其他器件进行数据传输时的一次数据传送量- 控制总线的宽度决定了

CPU对系统中其他器件的控制能力

:::danger

随着时代的发展,这种简单的总线结构逐渐被淘汰

:::

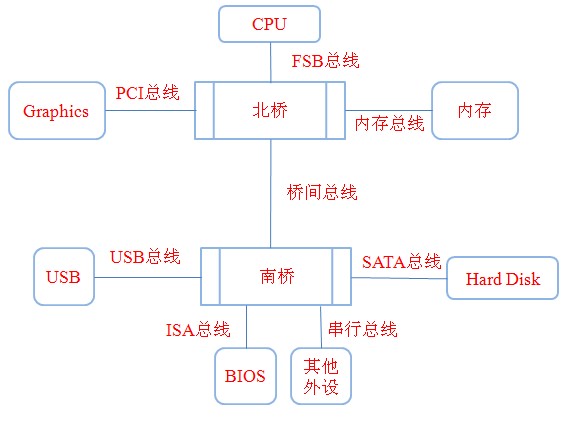

当今主流总线结构

主要部分:北桥(North Bridge也称Host Bridge)和南桥(South Bridge)。

- 北桥主要负责CPU和内存、显卡等的数据传送,

- 南桥主要负责I/O设备、外部存储设备以及BIOS之间的通信。

- 现在有些主板已经没有北桥了,因为芯片厂商已经把北桥所负责的功能直接集成到CPU中了

总线南桥北桥功能

- FSB总线:即前端总线(Front Side Bus),

和北桥之间的桥梁,

和北桥传递的所有数据必须经过

总线,

总线的频率直接影响到

访问内存的速度。

- 北桥:北桥是

和内存、显卡等部件进行数据交换的唯一桥梁,也就是说

想和其他任何部分通信必须经过北桥。北桥芯片中通常集成的还有内存控制器等,用来控制与内存的通信。现在的主板上已经看不到北桥了,它的功能已经被集成到CPU当中了。

- PCI总线:PCI总线是一种高性能局部总线,其不受

限制,构成了

和外设之间的高速通道。比如现在的显卡一般都是用的PCI插槽,

总线传输速度快,能够很好地让显卡和

进行数据交换。

- 南桥:主要负责

设备之间的通信,

要想访问外设必须经过南桥芯片。

1.2 CPU寻址和位数

1.2.1 CPU对储存器的读写

储存单元

储存器被划分成若干个储存单元,每个储存单元编号从

0开始,加入这个储存器有256个储存单元,那么储存单元的编号是0~255由于计算机的最小信息单位是bit. 而微型机储存单元可以储存一个**Byte**, 即8个二进制位。所以一个具有256个储存单元的储存器能够存储的信息量是256Bytes储存器的容量单位是字节(Bytes)

CPU对储存器的读写

对储存器的读写需要

类信息

- 储存单元的地址 ( 地址信息 ), 地址信息通过地址总线传输

- 器件的选择,读或写的命令( 控制信息 ),控制信息通过控制线传输

- 读或写的数据(数据信息), 数据信息通过数据线传输

CPU通过地址线告知我要访问号储存单元

CPU通过控制线发出内存读命令,选中储存器芯片,说明我要读取数据- 储存器将3号储存单元的数据8通过数据线传输入

CPU

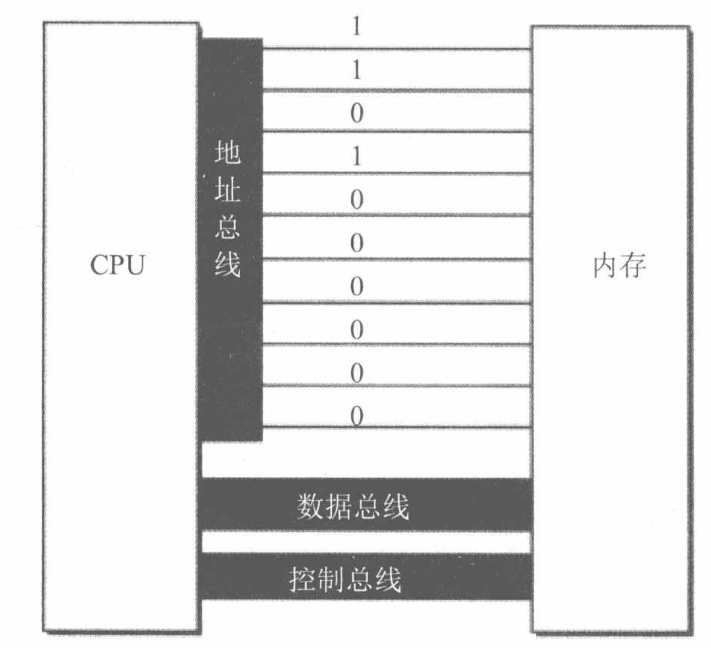

地址总线

CPU是通过地址总线来指定储存器单元的,地址总线上能传输多少不同的信息,**CPU**就可以对多少个储存单元进行寻址- 一个

CPU有N根地址线,可以说这个CPU的地址总线的宽度为N, 这样的CPU最多可以寻找个内存单元

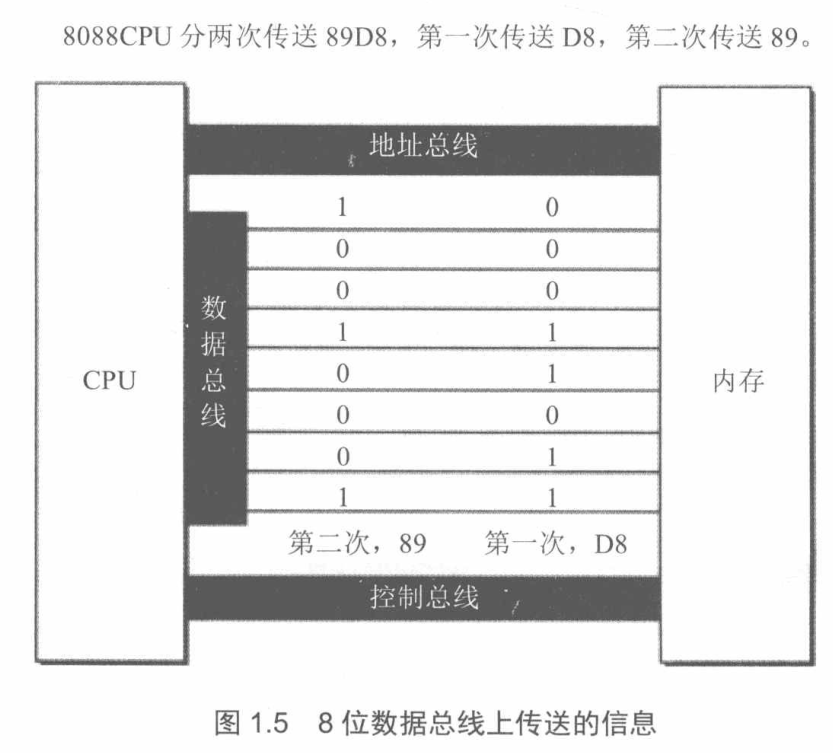

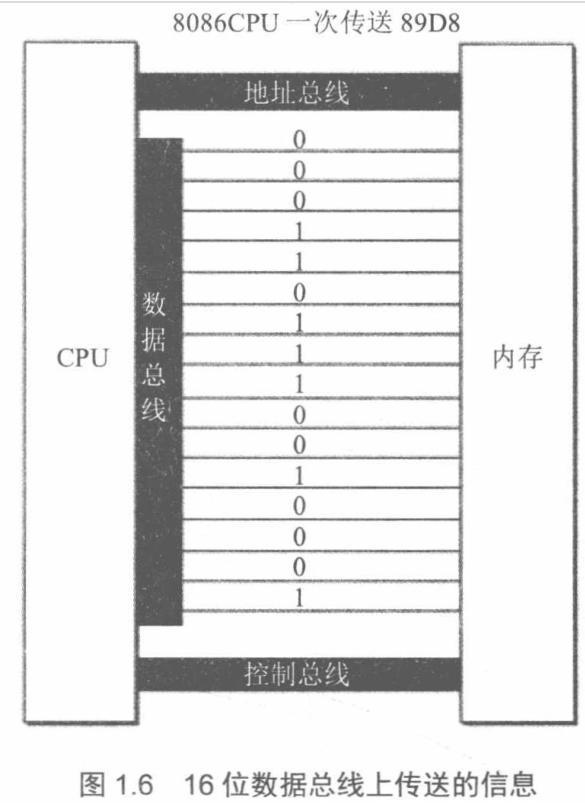

数据总线

与内存或者其他器件之间的数据传输是通过数据总线进行的。

- 数据总线的宽度决定了

和外界传输数据的速度,

根数据总线一次可以传送

位二进制数据(一个字节)。

根数据总线一次可传输两个字节

:::success

我们在传输一个16进制数据的时候,如89D8的时候,不同的数据总线宽度决定了不同的传输速度和方式

:::

控制总线

1.2.2 最大支持内存

:::success 在使用计算机时,其最大支持的内存是由 操作系统 和 硬件 两方面决定的。 :::

硬件因素

在计算机中

的地址总线数目 决定了

的 寻址 范围,这种由地址总线对应的地址称作为物理地址。 假如

有

根地址总线(一般情况下

位的CPU的地址总线是

位,也有部分

位的CPU地址总线是36位的,比如用做服务器的CPU),那么提供的可寻址物理地址范围 为

=4

(在这里要注意一点,我们平常所说的

位

和

位

指的是CPU一次能够处理的数据宽度,即位宽,不是地址总线的数目)。自从

位

出现之后,一次便能够处理

位的数据了,其地址总线一般采用的是

位或者

位(即

能够寻址的物理地址空间为

或者

)。 在

访问其它任何部件的时候,都需要一个地址,就像一个快递员送快递,没有地址他是不知道往哪里送达的,举个例子,

想从显存单元读取数据,必须知道要读取的显存单元的实际物理地址才能实现读取操作,同样地,从内存条上的内存单元读取数据也需要知道内存单元的物理地址。换句话说,

访问任何存储单元必须知道其物理地址。

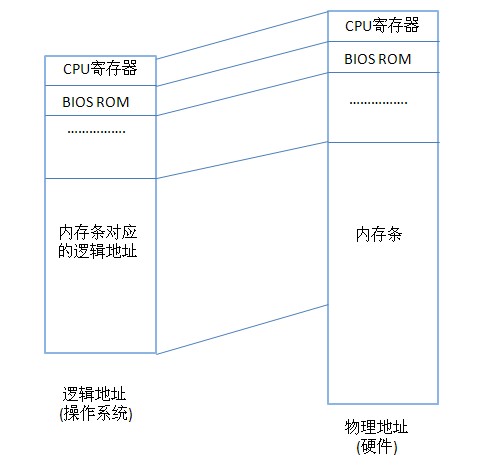

操作系统因素

用户在使用计算机时能够访问的最大内存不单是由

地址总线的位数决定的,还需要考虑操作系统的实现。实际上用户在使用计算机时,进程所访问到的地址是逻辑地址,并不是真实的物理地址,这个逻辑地址是操作系统提供的,

在执行指令时需要先将指令的逻辑地址变换为物理地址才能对相应的存储单元进行数据的读取或者写入(注意逻辑地址和物理地址是一一对应的)。

对于

位的

操作系统,其逻辑地址编码采用的地址位数是

位的,那么操作系统所提供的逻辑地址寻址范围是

,而在

架构下,采用的是内存映射技术(

),也就说将

逻辑地址中一部分要划分出来与

、

寄存器、

设备这些部件的物理地址进行映射,那么逻辑地址中能够与内存条的物理地址进行映射的空间肯定没有

了, 如下图所示:

所以当我们装了

位的windows操作系统,即使我们买了

的内存条,实际上能被操作系统访问到的肯定小于

,一般情况是

左右。假如说地址总线位数没有

位,比如说是

位,那么

能够寻址到

的物理地址空间,此时操作系统即使能支持

的逻辑地址空间并且假设内存条是

的,能够被用户访问到的空间不会大于

(当然此处不考虑虚拟内存技术),所以用户能够访问到的最大内存空间是由硬件和操作系统两者共同决定的,两者都有制约关系。 对于

位的操作系统,其逻辑地址编码采用的地址位数是

位,能够最大支持1T的逻辑地址空间。考虑一种情况,假如

是64位的,地址总线位数是

位,操作系统也是

位的,逻辑地址编码采用的地址位数也是

位,内存条大小是

,那么是不是内存条的

全部都能被利用了呢? 答案是不一定,因为这里面还要考虑一个因素就是内存控制器,内存控制器位于北桥之内(现在基本都是放在CPU里面了),内存控制器的实际连接内存的地址线决定了可以支持的内存容量,也就是说内存控制器与内存槽实际连接的地址线如果没有

位的话,是无法完全利用

GB的内存条的存储空间的。当然对于内存控制器这个问题几乎可以不用考虑,因为现在大多数的内存控制器至少都采用的是

位地址总线。

总结

:::success

的地址总线位数: 决定了

寻址能够访问到的物理内存的大小

- 一般我们说的

位的

, 一般说的是其使用的寄存器的位数

- 逻辑地址编码总线位数: 决定了最大支持的虚拟内存的大小, 比如某个64位操作系统的逻辑地址编码总线位数是

位, 则逻辑地址有

, 即最大支持

的虚拟内存,现在我买了

的内存条,说明操作系统能够利用的虚拟内存是

, 小于最大支持的虚拟内存大小.

- 往往逻辑地址的内存空间中有一部分是专门映射到

寄存器和

物理空间的,是用户无法直接利用的,所以往往操作系统无法完全利用内存条的大小

- 用户能够访问到的最大内存空间是由硬件和操作系统两者共同决定的,两者都有制约关系。 :::

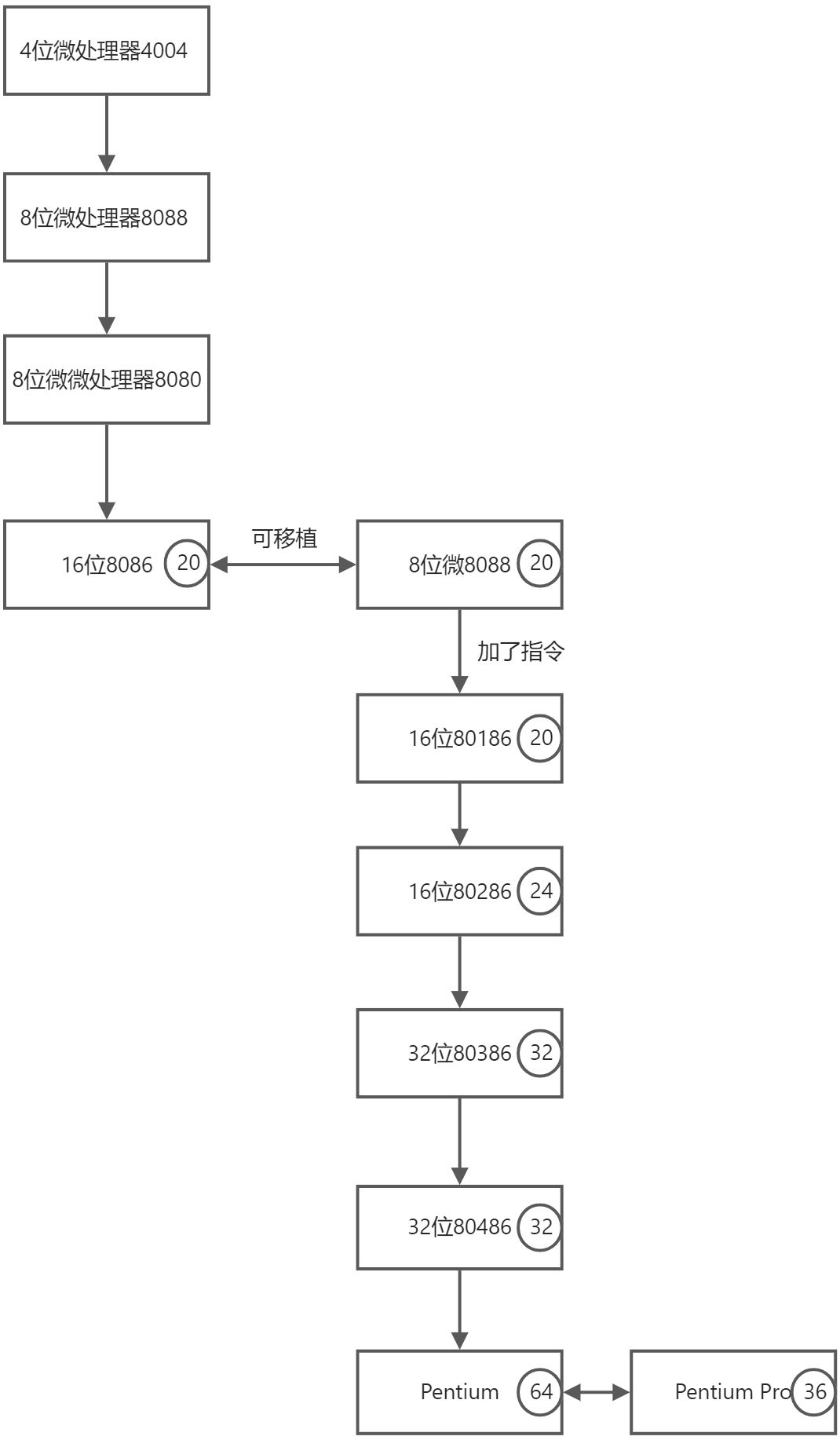

1.3 8086处理器 来由

笔记参考: https://www.cnblogs.com/zhaoyl/archive/2012/05/15/2501972.html

Intel CPU发展史

1.4 内存地址空间概述

各类储存器芯片

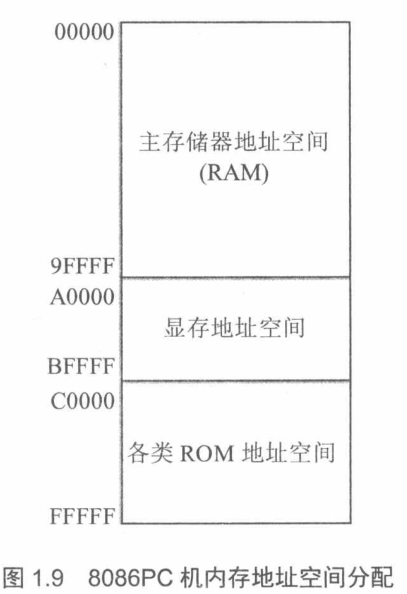

内存地址空间

上图中的储存器在物理上是独立的器件,但是也有共同点

- 都和

的总线相连

对它们进行读或写的时候都通过控制线发出内存读写命令

在操控它们的时候,把他们都当做内存来对待,把它们总的看做一个由若干储存单元组成的逻辑处理器,这个逻辑储存器就是我们所说的内存地址空间

:::success

上图中,右侧的物理储存器都被看做一个由若干储存单元组成的逻辑储存器,每个物理储存器在这个逻辑储存器中占有一个地址段,即一段地址空间。

:::success

上图中,右侧的物理储存器都被看做一个由若干储存单元组成的逻辑储存器,每个物理储存器在这个逻辑储存器中占有一个地址段,即一段地址空间。在这段地址空间中读写数据,实际上就是在相对应的物理储存器中读写数据。

:::

地址空间的大小受

地址总线款速的限制。

的地址总线宽度为

, 可以传送

个不同的地址信息, 即可以定位

个内存单元,则

的内存地址空间大小为