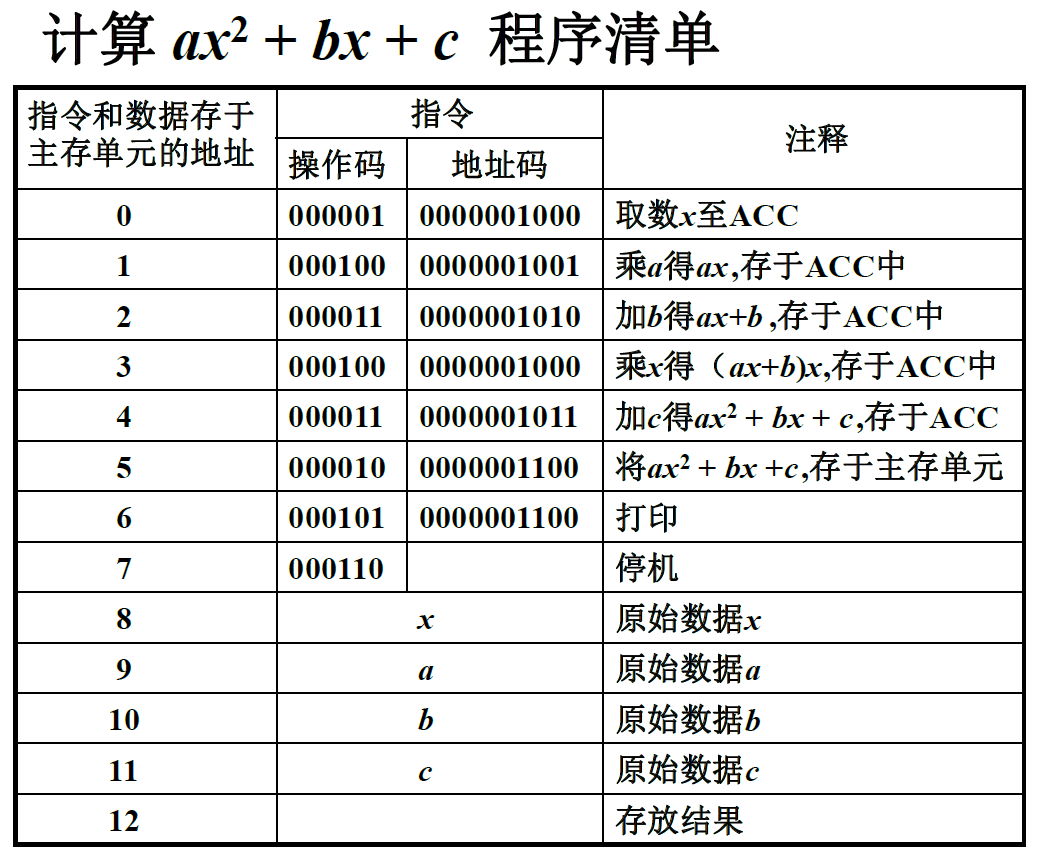

冯·诺依曼计算机的特点

存储程序通用计算机

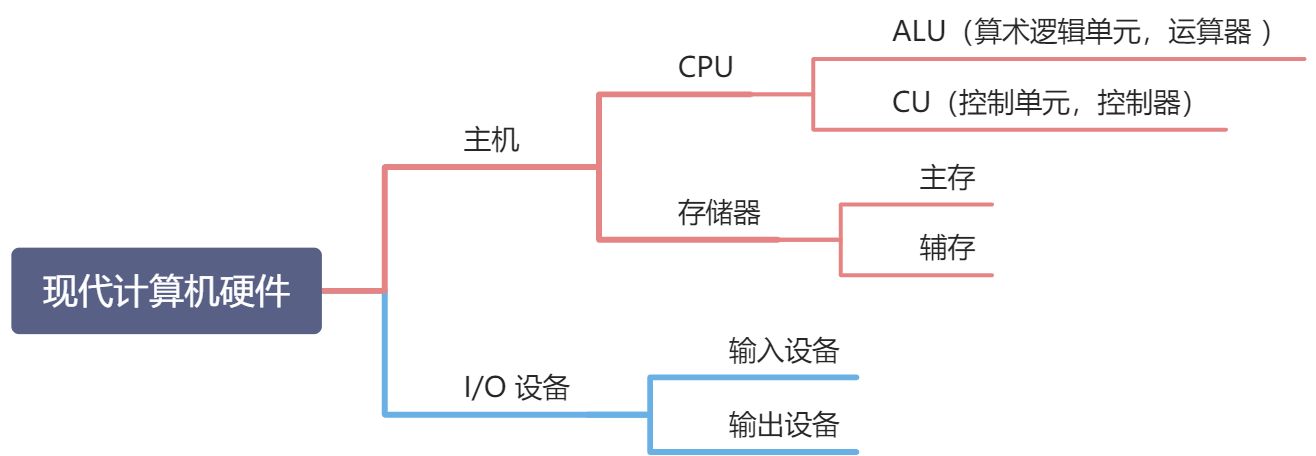

- 计算机由五大部件组成

- 指令和数据以同等地位保存于存储器,可按地址寻访

- 指令和数据用二进制表示

- 指令由操作码和地址码组成(操作码指明了该指令可执行的操作;地址码记录着操作数的内存地址)

- 存储程序(核心特点,是冯·诺依曼计算机的标志性特征)

-

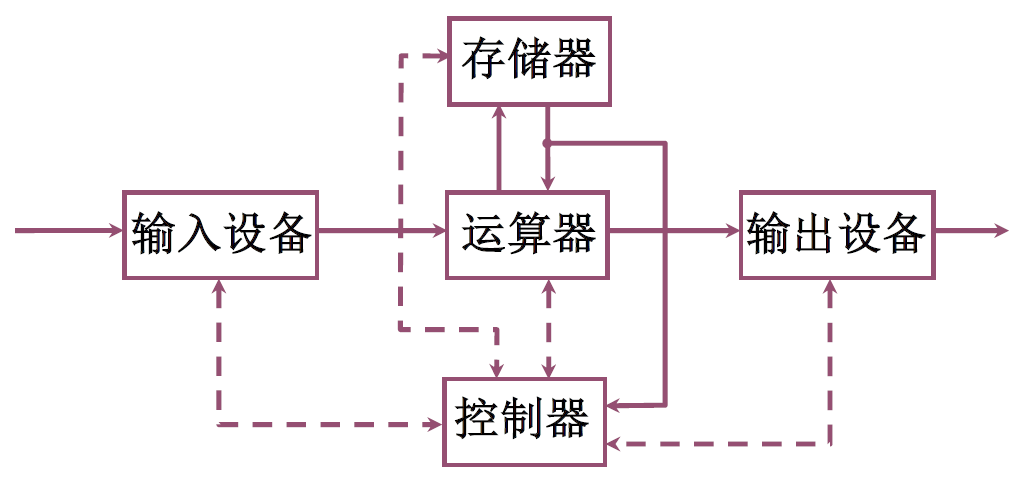

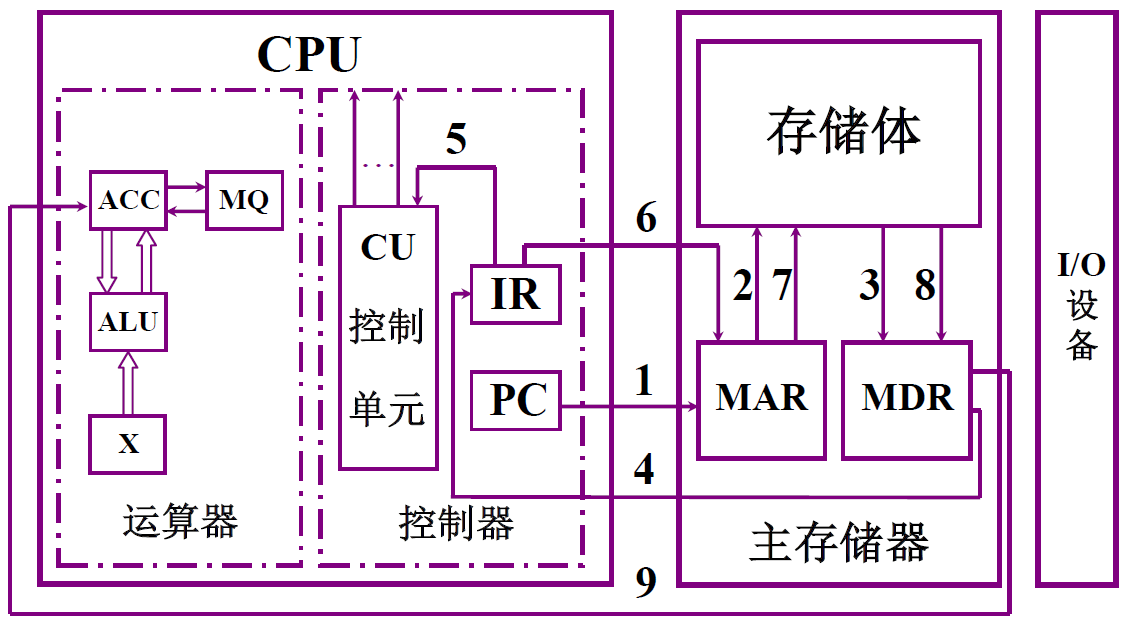

冯·诺依曼计算机的硬件框图

实线表示数据通路;虚线表示控制和状态反馈。

运算器:完成算术运算和逻辑运算

- 存储器:用于存储数据和程序

- 控制器:指挥控制程序的运行:完成指令的执行、完成指令间先后顺序的控制

- 输入设备:将信息转换成机器能识别的形式

- 输出设备:将结果转换成人们熟悉的形式

冯·诺依曼计算机在硬件上的缺陷: 以运算器为中心,繁忙的运算任务将成为制约计算机性能的瓶颈; 不具有层次化的特征。

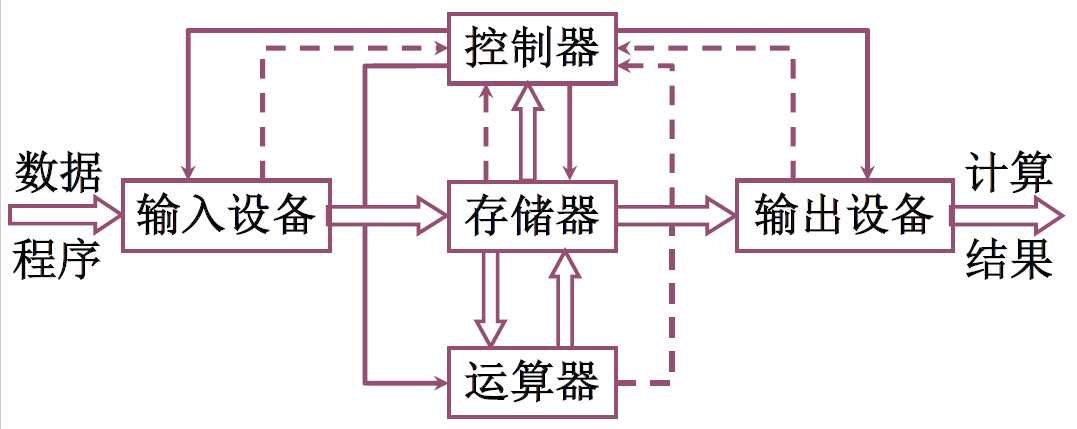

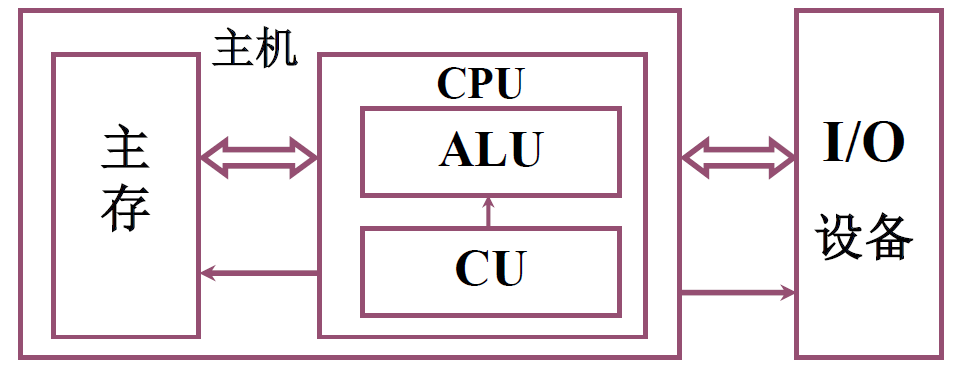

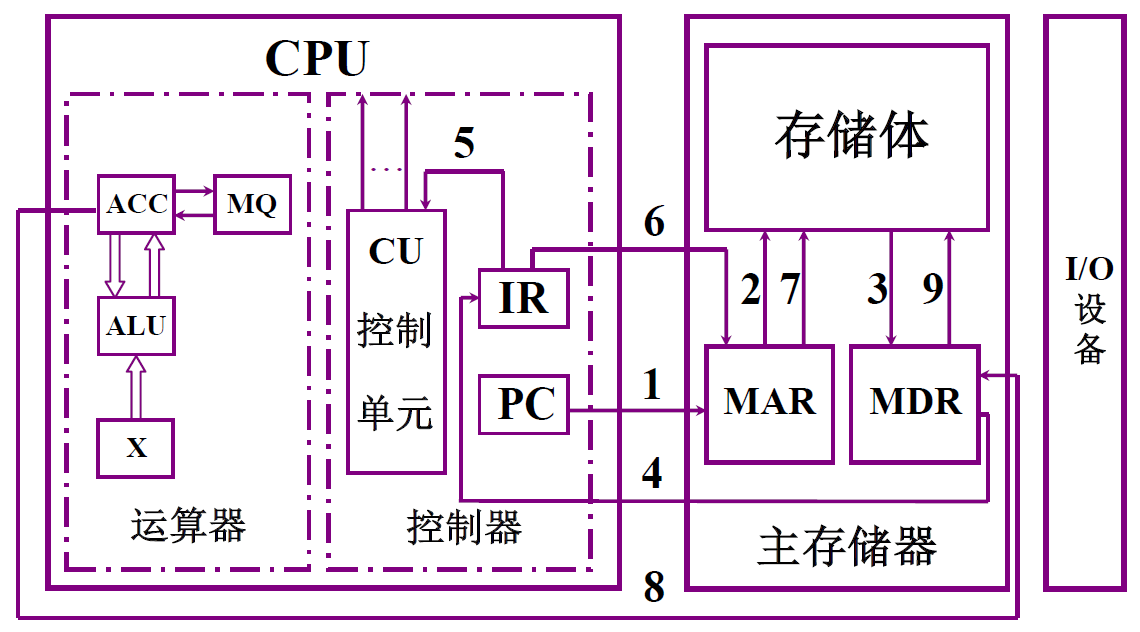

以存储器为中心计算机的硬件框图

把以运算器为中心的机器改进成以存储器为中心的机器,实现输入/输出设备与存储器间信息的直接交换。

条形线和实线表示数据通路;虚线表示控制和状态反馈。

现代计算机的硬件框图

:::tips

管理系统复杂性的方法 2——3 Y 法则

:::tips

管理系统复杂性的方法 2——3 Y 法则

- 层次化(Hierachy):将被设计的系统划分为多个模块或子模块;

- 模块化(Modularity):提供明确定义 (well-defined) 的功能和接口;

- 规则性(Regularity):使模块更容易被重用。

:::

可计算性:一个以 D 为定义域,R 为值域的函数,若存在一种算法,对 D 中的任意一个给定的 x 都能得出 f(x) 的值,则称这个函数是可计算的。用问题是否具有可计算性,评估该问题的是否可以用计算机解决。

停机问题:判断任意一个程序是否会在有限的时间之内结束运行的问题。 等价于:给定一个程序 P 和输入 w,程序 P 在输入 w 下是否能够最终停止。

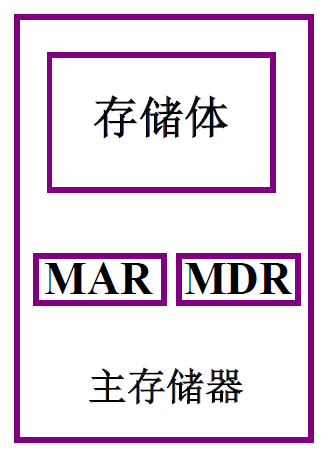

存储器

存储体是存储器的核心。

- 存储体中的存储单元由大量的存储元件组成。每一个存储单元都存放着一串二进制代码,这些代码的组合就是存储字;用存储字长表示存储字的位数;用存储单元的地址寻访数据。

- MAR 是存储器地址寄存器 (Memory Address Register

),记录了存储单元的个数、地址(编号),其位数和存储单元的个数有关。

- MDR 是存储器数据寄存器 (Memory Data Register),其位数和存储字长有关。

4 位的 MAR 可以表示从 0000 到 1111 的二进制数,可指向 24=16 个存储单元; 8 位的 MDR 可以表示从 00000000 到 11111111 的二进制数,可指向 28=256 种数据。即,对应的存储字长是 8。

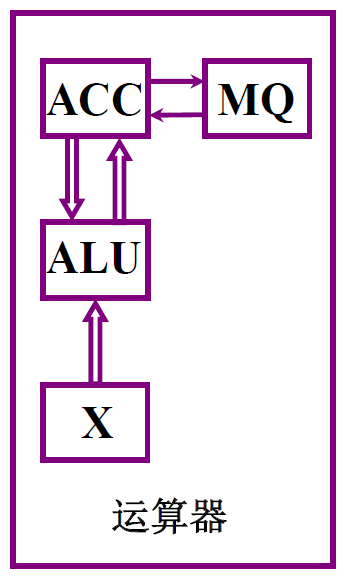

运算器

ALU (算术逻辑单元, Arithmetic Logic Unit)是运算器的核心。

- 算术逻辑单元 ALU 是一种可对二进制整数执行算术运算或位运算的组合逻辑数字电路。它通常是一个组合电路,其特点是若输入撤销,会相应撤销输出结果。为了顺利实现运算功能,需要在 ALU 的输入端配合寄存器实现对参与运算的数据进行存储。

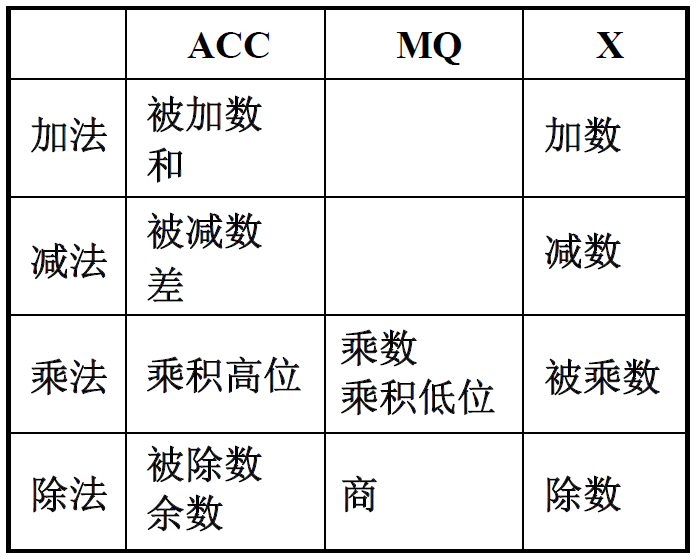

- X 为操作数寄存器。

- ACC(Accumulator, 累加器 A)一个专门用于存放操作数或运算结果的二进制 8 位寄存器。

- MQ 为乘商寄存器,能够进行乘、除运算,保存运算结果的低位(乘法运算结果的长度将增长一倍)。

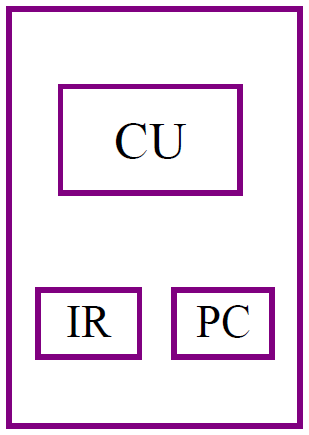

控制器

控制器用于解释指令,并保证指令的有序执行。控制单元 CU 是其核心。

一条指令的完成包括了指令的提取、分析和执行 3 个步骤。分别由控制器中的 PC(程序计数器)、IR(指令寄存器)和 CU(控制单元)完成。

- PC(程序计数器)保存了当前指令的地址,为了可以找到下一个指令的存储地址,PC 还具有计数功能。

- IR(指令寄存器)存储了当前即将执行的指令。

运算器、控制器、存储器共同构成了计算器的主机。

指令在主机上的实现过程

取数指令的实现

步骤 1~4:指令的提取

步骤 5:指令的分析

步骤 6~9:指令的执行

存数指令的实现

步骤 1~4:指令的提取

步骤 5:指令的分析

步骤 6~9:指令的执行

计算机硬件的主要技术指标

机器字长

CPU 一次能处理数据的位数,一般与 CPU 中寄存器的位数一致。

机器字长与机器性能呈正相关。

运算速度

用吉普森法衡量计算机的运算速度:根据每条指令的频率,计算指令执行时间的加权平均值。 用 CPI 法,每条指令所需的时钟周期衡量计算机的运行速度。 其他方式:

- MIPS:每秒执行指令的数目(指令/百万条)

- FLOPS:每秒浮点运算次数

主频

CPU 的时钟频率。主频和实际的运算速度有关系,但并不是一个简单的线性关系。还与指令的时钟周期、指令中包含的逻辑操作的个数有关。

核数、核支持的线程数

CPU 上的 CPU 核心数;CPU 能同时并行处理的任务数。

存储容量

主存容量

辅存容量

字节数。